I enjoyed reading Eric Esteve’s article “ French Tech at CES, 2nd country after USA with 274 Start-Up at Eureka Park!” It brought back happy memories of my time at EVE until Synopsys purchased it in 2012.Here is another intriguing story by a French startup named VSORA and founded by Khaled Maalej with a team of scientists and engineers. Not new to the French high-tech landscape, Khaled and team already reached success in a previous enterprise named DiBcom when it was acquired by Parrot, a dronecompany, in 2011. DiBcom was the leading providing of integrated circuits for mobile digital TV receivers incorporated into cell-phones, cars and PCs.

This time the team came up with a rather interesting idea.Digital Signal Processors (DSP) have been around for about four decades and by now they are ubiquitous in the semiconductor industry, used for image and audio processing, in communication and mobile applications, lately in automotive designs, essentially everywhere there is a need to elaborate digital signals. Today DSP designs are by far more complex and advanced than the pioneering implementations introduced by TI, AMD, NEC, and others in the late 1970’s. Still, all current offerings meet the need for ever growing processing power via one or more DSP co-processors: the higher the processing power requirement, the more th eco-processors. All well and good, but co-processors are essentially hard-wired algorithms. Any change to an algorithm, no matter how small, forces the DSP engineers to re-spin the hardware. A costly proposition with a very lengthy design-iteration-time (DIT) in the ballpark of one month or longer.

Based on their previous experience at DiBcom, the team conceiveda DSP architecture that eliminates the co-processors. Instead, they devised a flexible fabric built on a matrix of multiple DSP cores they call Multi-Core Signal Processors (MSP). Each core can be configured and optimized to perform a specific task. You can size the memory assigned to each core, tune the processing power, that is, select the number of arithmetic-logic-units (ALU),or adjust the floating point accuracy. For example, a DSP performing MiMo combinations requires different computation accuracy and rather higher processing power than one performing signal synchronization.

But this is not all there is to it. Vsora went a step,actually two steps further.

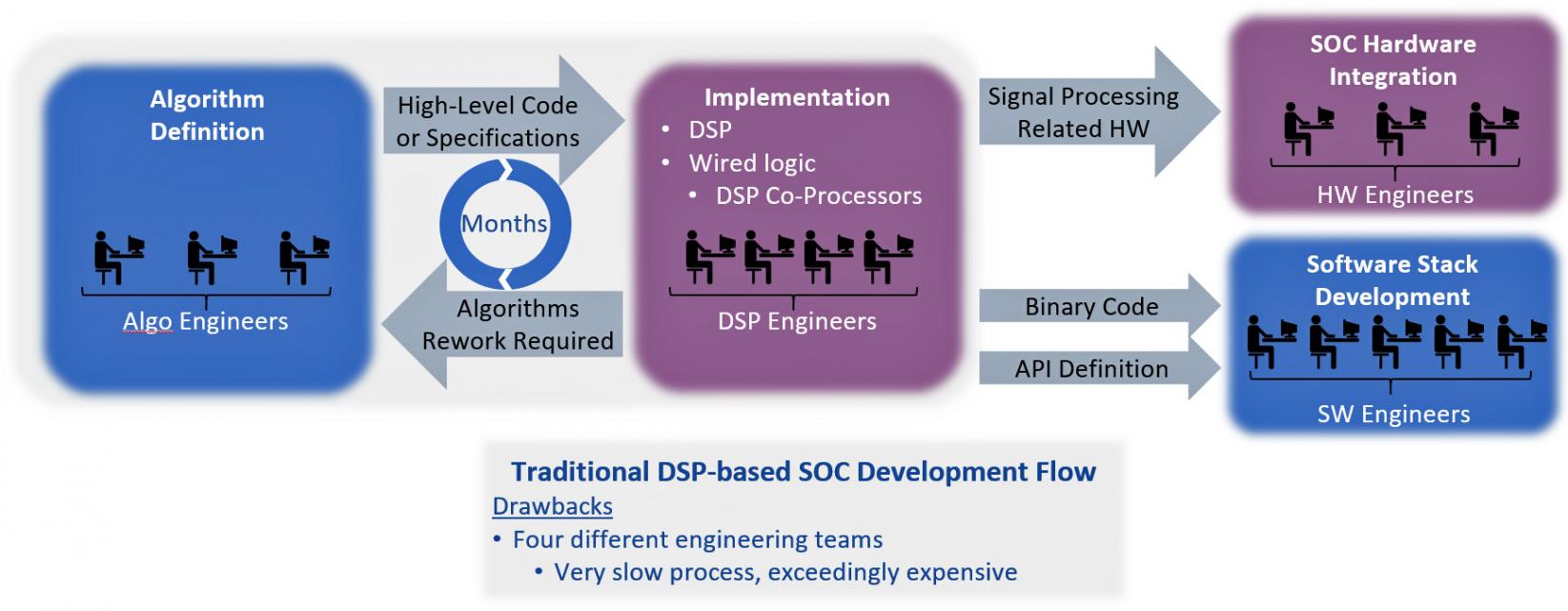

In an SoC design that includes an embedded DSP, for example a base station for a wireless application, the traditional development process involves four different design teams. First, the signal processing team, comprised of highly specialized engineers, defines an algorithm at high level of abstraction, commonly using Matlab-like coding. Once pleased with the results,they pass their creation on to the DSP design team to implement it either on the DSP or, when not feasible, in one or more co-processors. The two teams come from different backgrounds, possess different skills, use different development tools and methods, and habitually mis-communicate blaming each other. The scenario leads to multiple iterations between them until they agree on a result. The real problem is, each iteration may take weeks.

Once the DSP design is satisfactory, it is dispatched to the SOC hardware team that incorporates it into the SoC, and to the embedded software team that develops the supporting software stack.

Vsora envisioned a development environment that unifies the two DSP teams into the algorithmic team, giving them the tools to fine tune the algorithms until ready to be deployed in the SoC. They can perform “what-if”analysis, try different configurations, size each core for performance, power, orarea, generate multiple version of the DSP and compare them without implementing the actual hardware. Once pleased with the results, they forward the MSP to the SOC hardware and software development teams. The approach eliminates the detrimental iterations and accelerates the development schedule by few months.

As a cheery-on-the-cake, the team is also setting up the VSORA MSP development environment on the Amazon Web Services FPGA (AWS-F1) cloud. Engineers will be able to access the VSORA development environment and fine tune their algorithms while mapping it directly to the DSP. They will be able to reduce the simulation time of the implemented DSP by factor of 10s compared to simulation of the algorithmic model running on a PC, and eliminate the risk that abstract and implemented models may differ. Signal processing engineers will be able to define and implement their algorithms and verify them on a “prototyping-like”platform within minutes. This leads to better system/cost optimization at the early stage of the project and avoid significant upfront investments to setup a traditional development environment.

The upcoming 5G standard, heavily reliant on DSP technology, is posing new and steep challenges to the engineering community,stressing the traditional DSP development flow. The adoption of millimeter waves, MIMO, and other advanced technologies requires lots of processing power,creating a golden opportunity for the VSORA approach.

Recently VSORA closed their first round of funding from Omnes Capital, Partech Ventures, and few Angel Investors.Definitely, there must be something unique in the DNA of the French engineering community.

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry