Hardware emulation arose as a necessity out of the needs of the eighties. By the mid-1980s, semiconductor designs had outgrown the practical limits of gate-level simulation. Gate-level simulation delivered accuracy, but at glacial pace; silicon prototypes performed at real-speed but arrived far too late. The industry needed… Read More

Author: Lauro Rizzatti

The Great Divide: A Tale of Three Hardware Emulation Architectures

From Wooden Boards to White Gloves: How FPGA Prototyping and Emulation Became Two Worlds of Verification… and How the Convergence Is Unfolding

FPGA prototyping and hardware emulation originated from two independent demands that emerged at roughly the same time, namely, the necessity to implement digital designs in reconfigurable hardware. This was conceivable given the newly introduced field programmable gate array (FPGA) device.

Yet from the very beginning they… Read More

An AI-Native Architecture That Eliminates GPU Inefficiencies

A recent analysis highlighted by MIT Technology Review puts the energy cost of generative AI into stark perspective. Generating a simple text response from Llama 3.1-405B—a model with 405 billion parameters, the adjustable “knobs” that enable prediction—requires on average 3,353 joules, nearly 1 watt-hour (Wh). Once cooling… Read More

Hardware is the Center of the Universe (Again)

The 40-Year Evolution of Hardware-Assisted Verification — From In-Circuit Emulation to AI-Era Full-Stack Validation

For more than a decade, Hardware-Assisted Verification platforms have been the centerpiece of the verification toolbox. Today, no serious semiconductor program reaches tapeout without emulation or FPGA-prototyping… Read More

VSORA Board Chair Sandra Rivera on Solutions for AI Inference and LLM Processing

Sandra Rivera, a Silicon Valley veteran who is the former CEO of Altera, an Intel FPGA spinout, and long-time Intel executive, recently became Chair of the Board of Directors of Paris-based VSORA. VSORA, a technology leader redefining AI inference for next-generation data centers, cloud infrastructure and edge, is focused … Read More

Lessons from the DeepChip Wars: What a Decade-old Debate Teaches Us About Tech Evolution

The competitive landscape of hardware-assisted verification (HAV) has evolved dramatically over the past decade. The strategic drivers that once defined the market have shifted in step with the rapidly changing dynamics of semiconductor design.

Design complexity has soared, with modern SoCs now integrating tens of billions… Read More

Inference Acceleration from the Ground Up

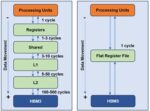

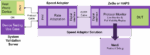

VSORA, a pioneering high-tech company, has engineered a novel architecture designed specifically to meet the stringent demands of AI inference—both in datacenters and at the edge. With near-theoretical performance in latency, throughput, and energy efficiency, VSORA’s architecture breaks away from legacy designs optimized… Read More

The Rise, Fall, and Rebirth of In-Circuit Emulation: Real-World Case Studies (Part 2 of 2)

Recently, I had the opportunity to speak with Synopsys’ distinguished experts in speed adapters and in-circuit emulation (ICE). Many who know my professional background see me as an advocate for virtual, transactor-based emulation, hence I was genuinely surprised to discover the impressive results achieved by today’s speed… Read More

The Rise, Fall, and Rebirth of In-Circuit Emulation (Part 1 of 2)

Introduction: The Historical Roots of Hardware-Assisted Verification

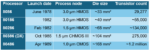

The relentless pace of semiconductor innovation continues to follow an unstoppable trend: the exponential growth of transistor density within a given silicon area. This abundance of available semiconductor fabric has fueled the creativity of design… Read More

Silicon Valley, à la Française

Since the fall of the Roman Empire, France has played a defining role in shaping Western civilization. In the 9th century, Charlemagne—a Frank—united much of Europe under one rule, leaving behind a legacy so profound he is still remembered as the “Father of Europe.” While Italy ignited the Renaissance, it was 16th-century France… Read More

Solving the EDA tool fragmentation crisis