On the last day of DAC 2025 I met with Chris Morrison, VP of Product Marketing at Agile Analog, to get an update. Their company provides Analog IP, the way you want it, and I knew that they had internal tools and a novel methodology to speed up the development process. This year they have started talking more about their internal IP automation tool, Composa.

Why use an analog IP automation tool?

Chris told me that there’s a list of challenges with conventional analog design: shortage of analog designers, too many processes and options, advanced nodes are difficult with new parasitics, and manual analog design is way too slow. Their answer was to address these challenges by using analog IP automation.

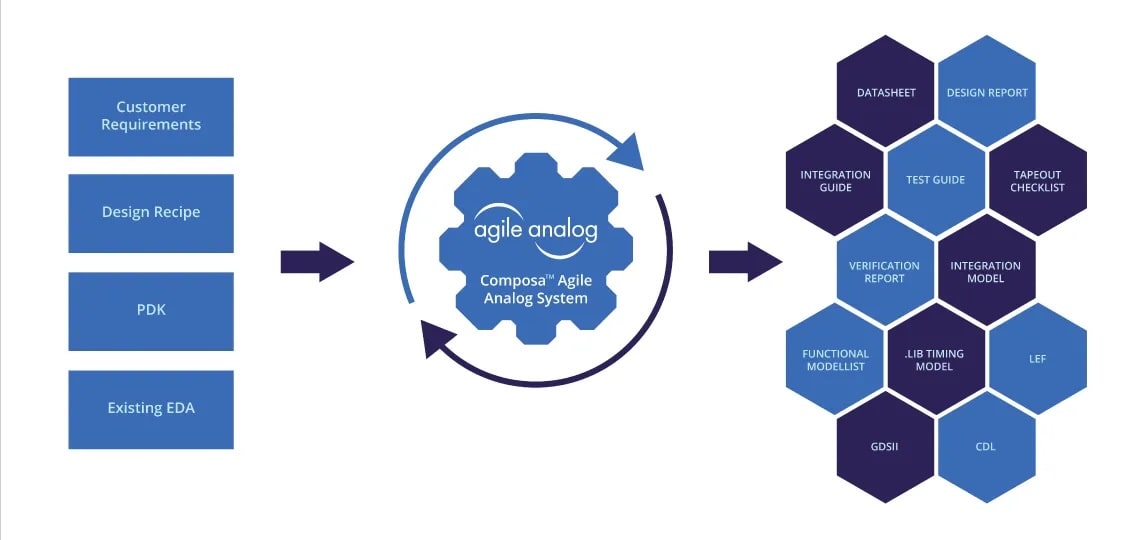

The approach is to combine Analog experts inside of the company along with SW developers to auto-generate schematics for IP. Their Composa tool works with OpenAccess, the API from the Si2 OpenAccess coalition. Composa users first define their requirements, like SNR, supply rails, bandwidth and other specifications. Then, there are a set of common analog building blocks, elements with their own characteristics that are combined to define the new IP. For example, an Analog to Digital Converter (ADC) needs a sample switch, input buffer and other blocks. These lower-level blocks are combined, a PDK is selected for a specific process, then the tools optimize the transistor W/L sizes using math equations.

A traditional approach to circuit sizing involves running lots of SPICE simulations, but Composa uses a much faster method of equation-based device sizing. With circuits that have feedback, then some SPICE runs could be used. The optimization process with Composa is not CPU intensive at all, typically requiring only a few minutes of CPU time to come up with the proper device sizes to meet your specifications. Full verification of the analog IP is done with a traditional flow, including many Monte Carlo simulations. There’s little, or no, manual-tweaking of device sizes required to meet your specs.

With Composa the engineers at Agile Analog can get to the exact specs for an IP block in minutes, not days or weeks of manual efforts. Even changing to a different PDK will show new results in just a few minutes.

Customers of Agile Analog span a broad range of sectors and applications: Power Management ICs (PMIC), data converters, chip health and monitoring, PVT, IoT, defense, , security, anti-tamper IP, voltage glitching, clocking attacks, electromagnetic injection. Defense customers could be designing at 165nm or 130nm process nodes, datacom at 3nm, so Composa creates analog IP for quite a wide spectrum of processes.

Digital designers have used logic synthesis to retarget process nodes for decades and this is now possible with analog design. If a customer wants a new oscillator, then Composa can be used to create a schematic and layout. Composa is an expert system – it is repeatable, human understandable, and device sizing is not a probability problem.

Composa is a no-code system for users, its parameters are typed in a YAML script to configure what you want. Internally they just fill in the YAML to control each IP block generator. Composa has changed over time by expanding the element library, and verifying that it works across all PDKs, including some tuning for a new PDK. The Composa tool has created some 60 new IPs in the last 2 years..

Analog security IP is of special interest for the Agile Analog team as security has become a critical requirement for every SoC being developed. The company believes that it can offer differentiated anti-tamper solutions that are complementary to other providers of RoT (Root of Trust) and cryptographic engines, delivering value at the subsystem level with their security IP offerings. Another focus area is their data conversion IP solutions. They are working with a strategic customer to deploy their 12 bit ADC on the latest TSMC nodes.

Agile Analog is based in the UK, while Krishna Anne, the CEO is in the valley. 2025 has been another good year of revenue growth at the company. Visit their website for more product information. They have direct sales in US and Europe, with some distributors in Taiwan, Korea and China. Catch up with the Agile Analog team at the GlobalFoundries and TSMC events.

Summary

Analog IP is in high demand, but the older manual methods to hand-craft IP just take too long and require expert experience. Agile Analog has a different approach using their Composa tool to automate the IP creation process, with a library of analog building blocks. What used to take days or weeks of engineering effort now can be accomplished in minutes with this new methodology, significantly reducing the complexity, time and costs associated with traditional analog IP.

Related Blogs

- Agile Analog at the 2025 Design Automation Conference #62DAC

- CEO Interview with Krishna Anne of Agile Analog

- 2025 Outlook with Christelle Faucon of Agile Analog

- Overcoming obstacles with mixed-signal and analog design integration

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.