Many know Arteris as the “network-on-chip”, or NoC, company. Through acquisitions and forward-looking development, the footprint for Arteris has grown beyond smart interconnect IP. At DAC this year, Arteris highlighted its latest expansion with a new SoC integration automation product called Magillem Packaging. The announcement focused on substantial new capabilities to simplify and speed up the process of building advanced chips used in everything from AI data centers to edge devices. I had an opportunity to visit Arteris at DAC and to speak with some of the executives there. Let’s examine how Arteris simplifies design reuse with Magillem Packaging.

The Announcement

The announcement made at DAC pointed out that chip design is becoming increasingly complex, with more components, higher performance demands, and tighter timelines. There is no argument there. The release states that Magillem Packaging helps engineering teams work faster and more efficiently by automating one of the most time-consuming parts of the design process: assembling and reusing existing technology.

Going deeper, Magillem Packaging enables IP teams to quickly and reliably package and prepare hundreds or even thousands of components for integration into a single chiplet or chip design, including new, existing, or third-party IP blocks.

Some of the key capabilities of this new product from Arteris are:

- IP reuse with comprehensive IP, subsystem, and chiplet packaging in a reusable format, including configuration, implementation, and verification for incremental and full packaging with a proven methodology.

- IEEE 1685-2022 generation is correct-by-construction without requiring any pre-requisite IP-XACT expertise. Standard compliance and data consistency are ensured by construction and assessed with a built-in Magillem checkers suite.

- Scalable and fully automated generation of IP packaging for reused and new IP blocks, with support for legacy 2009 and 2014 versions of the IEEE 1685 standard, with intuitive graphical editors enabling fast viewing and editing of IP block descriptions.

Ecosystem Support

Arteris technology is agnostic and works across the ecosystem to ensure ease of integration for end customers. Among those voicing support for the new capability are:

Andes Technology

“Andes Technology is recognized for our comprehensive family of RISC-V processor IP and customization tools that empower customers to easily differentiate their SoC designs,” said Marc Evans, director of business development & marketing at Andes Technology Corporation. “The latest IP-XACT 2022 specifications enable structured automation, optimizing IP packaging and integration. Magillem Packaging complements Andes’ commitment to streamlined workflows, enabling faster and more reliable SoC development.”

MIPS

“The MIPS Atlas portfolio is engineered for high-efficiency compute in autonomous, industrial, and embedded AI applications, where rapid integration and design reuse are critical,” said Drew Barbier, VP & GM of the IP Business Unit at MIPS. “Arteris Magillem Packaging, with its automation of IP-XACT 2022-compliant packaging and support for industry standards, aligns with customer needs to accelerate SoC development. Together, we empower customers to streamline IP integration, reduce design complexity, and bring innovative silicon to market faster.”

More From the Show Floor at DAC

While visiting Arteris at DAC, I had the opportunity to discuss this announcement with two key members of the management team in more detail.

Insaf Meliane is a product management and marketing director at Arteris. Before joining the product team, she was a field application manager, supporting customers with complex SoC design integration. She holds an engineering degree in microelectronics option system-on-chips from École Nationale Supérieure d’Electronique et de Radioélectricité de Grenoble.

Andy Nightingale is the VP of product marketing at Arteris. Andy is a seasoned global business leader with a diverse engineering and product marketing background. He’s a Chartered Member of the British Computer Society and the Chartered Institute of Marketing and has over 35 years of experience in the high-tech industry.

We began by discussing the overall reaction to Magillem Packaging at DAC. Interest was high, and reactions were quite positive. There has been an increase in momentum for IP-XACT. The features of the latest IP-XACT 2022 version have helped. Arteris has been a major supporter of this standard, and the new capabilities delivered by Magillem Packaging have helped as well.

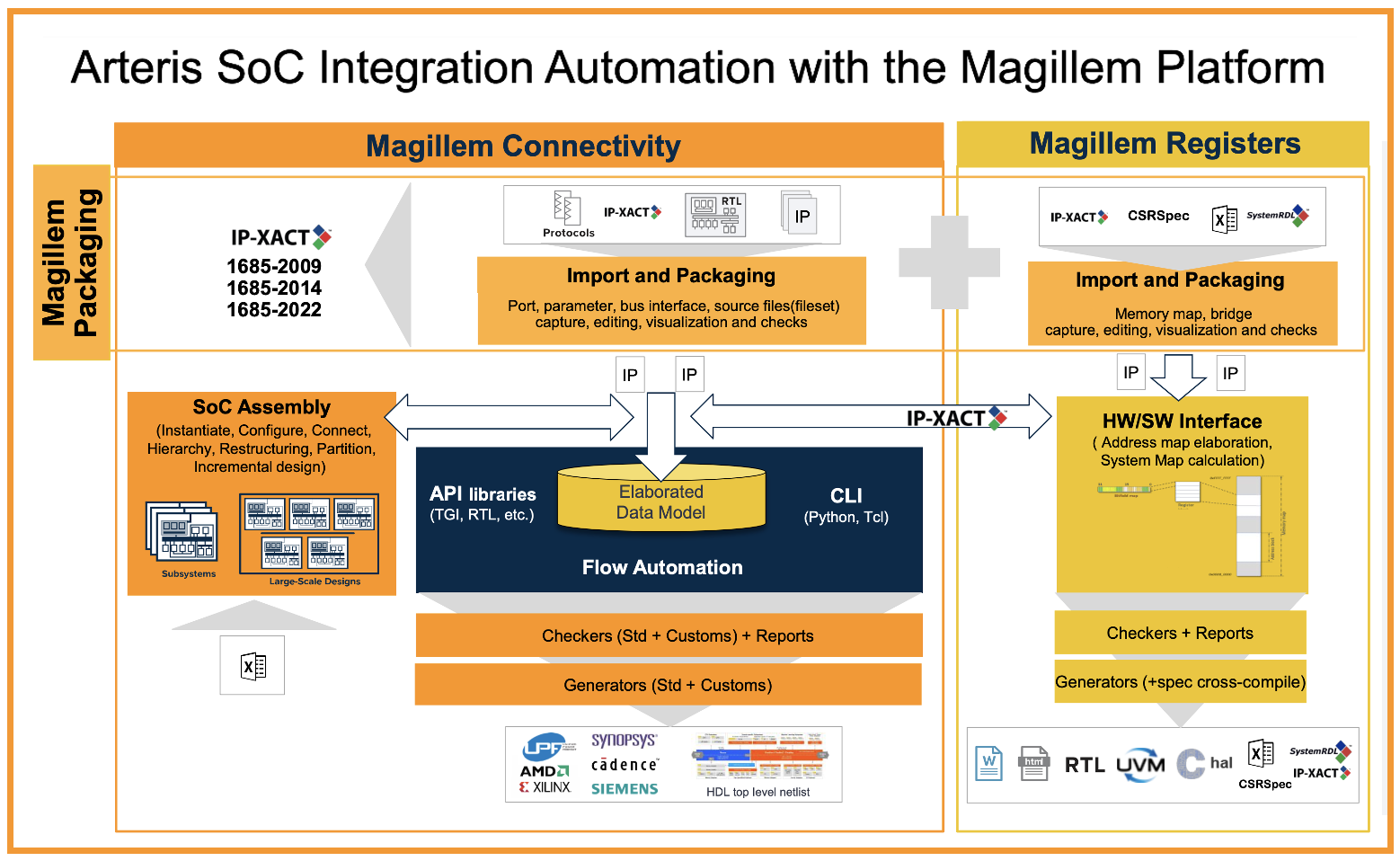

Insaf explained that Magillem Packaging leverages the Arteris Magillem Platform by integrating parts of Magillem Connectivity and Magillem Registers to create the new product. The figure below provides an overview of the platform and how the pieces fit together. Insaf described the significant benefits this new product delivers. The image at the top of this post includes a summary of the key benefits.

She went on to explain the significant automation provided by Magillem Packaging. Keeping track of a complex system’s connectivity and interface requirements is a daunting challenge. With Magillem Packaging, these details are automated and verified as correct. She described how the new version of IP-XACT 2022 delivers substantial new capabilities, and Magillem Packaging leverages all these capabilities in an automated way. There is no need for the user to learn all those details.

She summarized some of the key benefits of the new tool as follows:

- Effortless, scalable automation: handles both legacy and new IPs for a smoother assembly, faster scaling for large designs with less risks, reducing the potential for human error, and increasing efficiency

- Single source of truth specification: ensures consistency across various uses, bringing up immediate collaboration across the relevant teams, and catching errors before they become costly roadblocks.

- Safely, easily, and quickly adapt to changes: with a robust, rapid, highly iterative design environment. It reduces effort and rework to focus on core business, leverage technical expertise, and dream up what comes next.

She also pointed out that Arteris is working with various IP providers to ensure full support for IP-XACT 2022 so customers can fully enjoy its benefits.

I then explored the bigger development programs at Arteris with Andy. He described some of the joint efforts between the NoC and Magillem Connectivity teams. This work improves the target system’s overall connectivity management and helps with the complex verification tasks, thanks to the consistent views created across simulation, FPGA, emulation, synthesis, and fault injection.

Andy couldn’t disclose too many details about upcoming enhancements, but this is an area to observe going forward, and Arteris is leading the charge.

We concluded our discussion with a broader view of multi-die design requirements. On SemiWiki, you can learn more about how Arteris responds to these challenges. Some eye-opening statistics about Arteris technology include that over 200 customers have completed 860 design starts and shipped about 3.75 billion units.

To Learn More

Managing all the information associated with the new heterogeneous semiconductor systems under development can be a considerable challenge. One error can jeopardize the entire project. If these issues keep you up at night, you want to learn more about what Arteris is doing with its Magillem technology. You can read the press release announcing Magillem Packaging here. And you can learn more about this new product here. And that’s how Arteris simplifies design reuse with Magillem Packaging.

Also Read:

Arteris Expands Their Multi-Die Support

How Arteris is Revolutionizing SoC Design with Smart NoC IP

Podcast EP277: How Arteris FlexGen Smart NoC IP Democratizes Advanced Chip Design with Rick Bye

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.