Whether it is fully autonomous driving, or wrinkle-free fabric, or ambient energy harvesting for powering electronic devices, each industry is chasing after its respective ultimate goal. For the semiconductor design industry, its goal is the capability to generate complete chip or IP in executable format from a high-level behavioral description. It is interesting to note that many decades ago, when schematic capture was the predominant way of specifying designs, many companies had special projects to work on behavioral language compilers. Of course, even a very complex chip in those days was much, much simpler than even the simplest chip of today.

Those were the days when EDA tools were developed in-house at IDMs and ASIC companies. The third-party EDA industry as we know today was in its nascent stage. The primary motivation for the IDMs and ASIC companies was to get the chip to production as quickly as possible. This meant that the special projects didn’t get the full-fledged investment and attention. Just as the chip complexities started growing rapidly, HDLs such as VHDL and Verilog started gaining fast traction. And of course, the third-party EDA industry started burgeoning as well. All the wonderful RTL-level tools from the EDA industry have come in handy to implement even the most complex of chips today.

Of course, the above progress has put a strain on a couple of areas. One is the manual conversion of the high-level specification of a design to VHDL or Verilog. And the other is the amount of effort/time taken for verification. Is there a way to kill two birds with one stone?

Has the time arrived? Can a tool be developed that can auto-generate RTL, SystemVerilog Assertions (SVA), UVM testbench/tests, C/C++ driver code, and documentation for an entire IP block or chip? If this tool deploys correct-by-construction methodology, wouldn’t that reduce the time and effort needed for verification? Or would it? Agnisys claims it would. Can we make that leap of faith? Even in the traditional flow using time-tested layout tools, layout is verified against the netlist using a LVS verification tool. Bring your questions to their booth at DAC 2022. Agnisys will be showcasing a demo of a tool that they have been building using crowdsourced inputs and trials.

The company says that this tool is the next step in its ever-increasing solution for specification automation. With register automation well established some years ago, Agnisys turned their attention next to sequence automation for both SystemVerilog/UVM and C/C++. They released a technology called iSpec.ai, available at https://www.ispec.ai, that deploys machine learning (ML) techniques to auto-convert English assertions into proper SVA. It can also convert SVA into English and convert English to a programming sequence. Agnisys created a library of IP for standard functions that generates the design, UVM testbench and tests, C/C++ code, and documentation. They even created a tool to connect the IP blocks together at the top level of an SoC automatically.

Agnisys’ vision is to fully automate specification to implementation across design and verification, software, and device drivers. With register automation, verification automation, and interconnect automation under their belt, they are now seeking to expand specification automation to cover complete IP cores. The idea is for a system architect to create a specification and then press a button to generate the entire IP in an executable format. The spec could cover state machines, datapaths, and more in addition to registers. The output of this tool is to include the RTL code, the UVM verification environment and testbench/tests, C/C++ driver code, and documentation. Anyone developing an IP, FPGA, ASIC, or SoC will find this capability of interest.

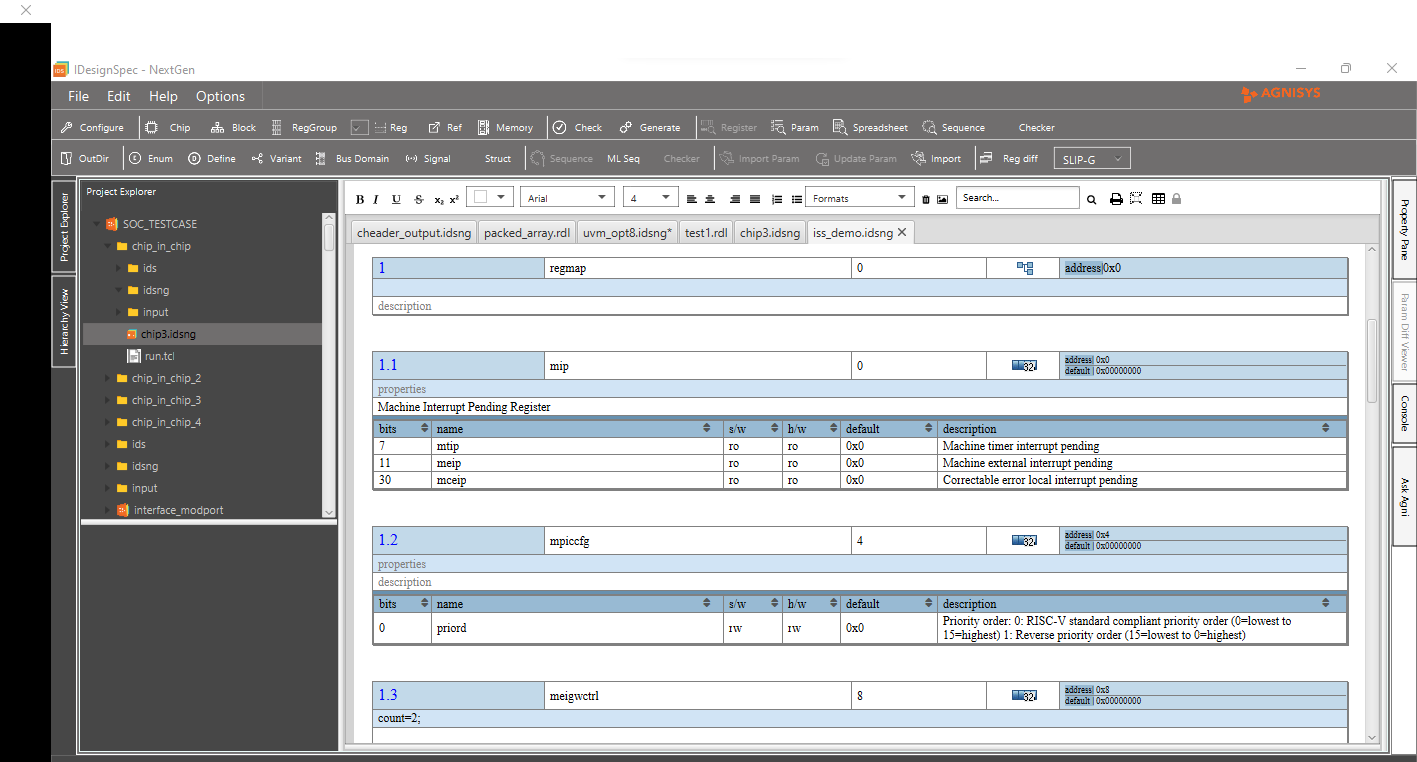

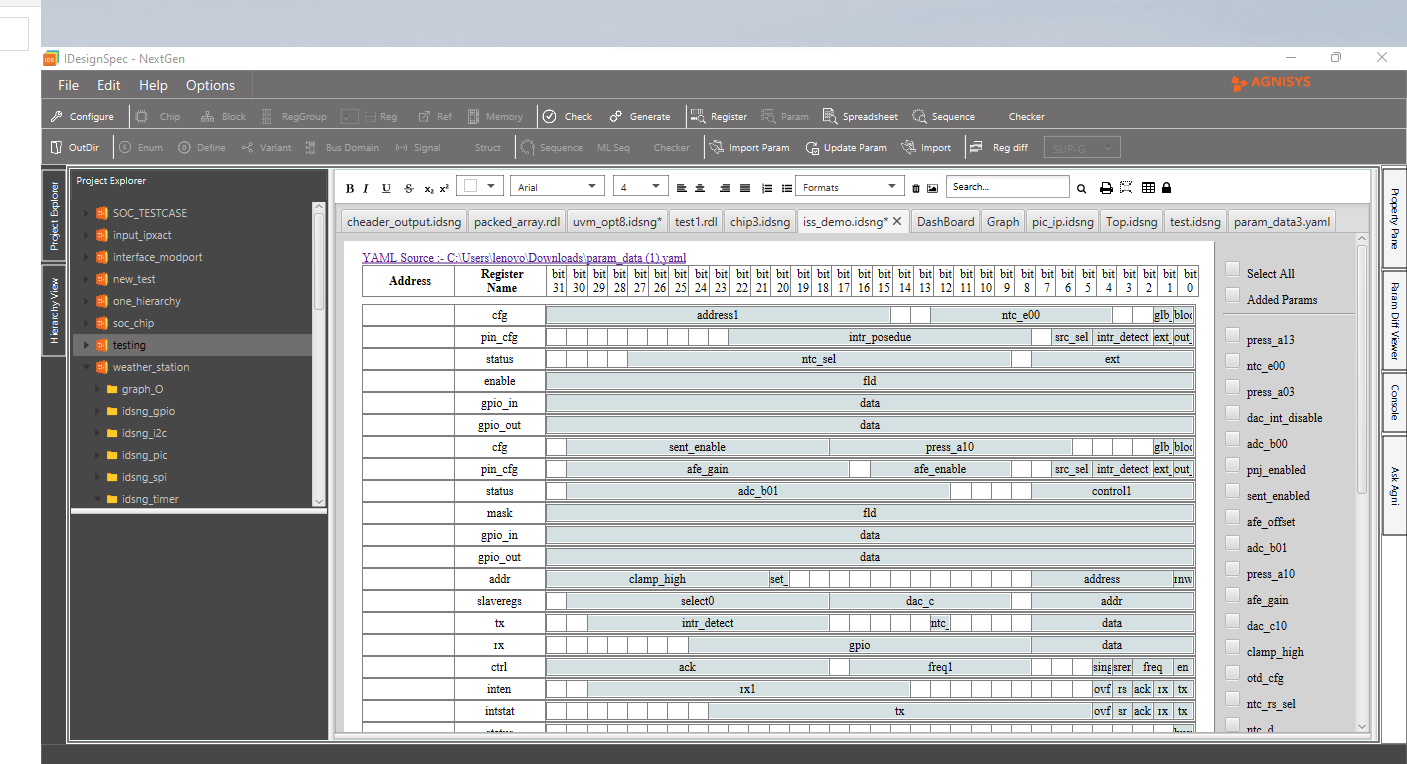

Sounds too good to be true? The only way to find out is to visit them at DAC, see their demo, ask questions, poke holes, and see if their story can hold water. Here are a couple of screenshots from the demo.

The tool capability may have to mature over time just as all of today’s greatest tools had to go through their own maturation process based on customers’ feedback. You can learn more about Agnisys here.

Given Agnisys’ track record, you can expect to see something interesting at their booth. So go check them out at booth number 2512 at DAC 2022 in San Francisco.

Also Read:

ISO 26262: Feeling Safe in Your Self-Driving Car

DAC 2021 – What’s Up with Agnisys and Spec-driven IC Development

Share this post via:

Siemens U2U 3D IC Design and Verification Panel