With EDA tool development in San Jose, Beijing and China, ProPlusis probably best known for their device modeling software called BSIMProPlus. At DAC I met with Lianfeng Yang, Ph.D. the VP of Marketing to hear about what’s new.

Lianfeng Yeng, ProPlus

Q: What is your tag-line this year?

Our tagline is, “From Nano-scale modeling to giga-scale”.

Q: What’s new in FastSPICE circuit simulation at ProPlus?

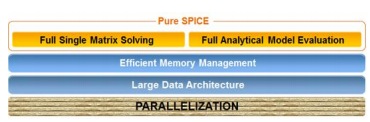

NanoSpice, it targets large scale simulation at SPICE accuracy. 50 million elements, 100 million elements for memory, 507 million elements for DRAM.

Traditionally memory designers would use a Fast SPICE tool, so now our NanoSPice can simulate that capacity now.

Q: How are you different than the BDA approach?

The simulation claims sound similar, but we haven’t run into the same customers yet competitively.

Q: Who is using NanoSpice?

The technology has been used by customers in other applications like NanoYield (SMIC).

NanoSpice engagements are ongoing.

Q: Can I do AMS simulation?

Yes, Verilog-A is supported with NanoSpice. No support for other languages.

Q: Can you talk about pricing?

Pricing: competitive.

Sales: Both perpetual and tbl.

Q: Which OS platforms do you support?

Linux.

For NanoSpice you can run with a simple licensing scheme to get the # of licenses that they want at an affordable price.

Q: How much RAM does NanoSpice use?

For memory about 14GB to simulate 507M elements in a DRAM design.

Q: When did ProPlus start?

ProPlus started in 2006, our offices are in San Jose, Beijing, Shanghai, Tokyo, Taiwan. Europe handled from the USA.

Q: What are the input and output formats to NanoSpice?

Netlist: HSPICE, Spectre, (not full Eldo).

Parasitic formats: DSPF,

Output: fsdb, pss format

Q: Can I run NanoSpice interactively?

NanoSpice is batch oriented, command line tool.

Q: What types of analysis are supported?

Analysis: DC, Tran, Tran nose, sweep, AC, sensitiviy analysis.

Noise characterization – 1/f noise, device noise, foundry-supplied noise models, noise characterization. We have a way to measure this noise on the wafer, 9812d version model. Able to measure the noise model, which then goes to CAD group creating the PDK models. Industry standard for 10 years now, just a new improvements.

Models: MOS, Bipolar, FinFET, SOI.

Q: Does ProPlus have any panel sessions at DAC?

Yes, our Panel – Learning the Secrets of DFY. Tomorrow at 1:30 at the Pavillion Panel, TSMC and GF, Nano Spice architect.

*lang: en_US

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center