We’ve all heard this claim: “Our FPGA synthesis tool produces better quality of results (QoR).” If you’re just hoping for a tool to do that automagically, you’re probably doing it wrong. Getting better QoR depends on understanding what an FPGA synthesis tool is capable of, and how to leverage what it tells you.… Read More

Synopsys @ #51DAC Must See!

Accelerating Innovation—that has been at the heart of Synopsys’ commitment to its customers for more than 25 years. As a leader in EDA and semiconductor IP, Synopsys’ software, IP and services help engineers address their design, verification, system and manufacturing challenges and accelerate their innovations. Since 1986,… Read More

Analog and Full Chip Simulation at Micron

IDM companies like Micronuse SPICE circuit simulators during the design phase in order to predict timing, currents and power on their custom IC chip designs at the transistor level. A senior memory design engineer at Micron named Raed Sabbahtalked today at a webinarabout how the embedded solutions group uses the FineSimcircuit… Read More

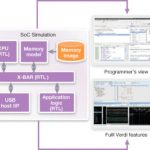

Hardware/Software Debug

One of the big challenges with modern SoCs is that they have a complex software component as well as the hardware itself being complex. Some aspects of the hardware can be debugged independently of the software and vice versa, but often it is not immediately clear whether the source of a problem is hardware, software or some interaction… Read More

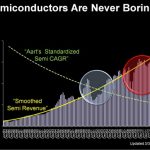

Designing Change into Semiconductor Techonomics

Every industry has famous thought leaders that can summarize where we’ve been and then paint a picture of where we’re headed towards in the future. Often they make statements that become industry expressions, like “Moore’s Law” or the “Internet of Things”. I think that if Synopsys… Read More

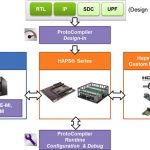

More knowledge, less time in FPGA-based prototyping

I recently published a post on LinkedIn titled “Sometimes, you gotta throw it all out” in reference to the innovation process and getting beyond good to better. A prime example has crossed my desk: the new ProtoCompiler software for Synopsys HAPS FPGA-based prototyping systems.

Last week, I spoke with Troy Scott, product marketing… Read More

Sebastian Thrun: Self-driving cars, MOOCs, Google Glass and more

Sebastian Thrun gave a fascinating keynote at SNUG last week. It didn’t have that much to do with IC design but he discussed 3 projects that he had been involved with. Anyone would be happy to have just one of these projects on their resume but he has all these (and more).

The first is the Google self-driving car. This project actually… Read More

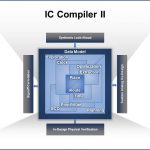

SNUG and IC Compiler II

I have been at SNUG for the last couple of days. The big announcement is IC Compiler II. It was a big part of Aart’s keynote and Monday lunch featured all the lead customers talking about their experience with the tool.

The big motivation for IC Compiler II was to create a fully multi-threaded physical design tool that will scale… Read More

AMS Verification and Regression Testing of SoC Designs

Digital verification engineers on SoC designs have adopted many techniques to help ensure first silicon success: using compiled simulators, constrained random test, simulation farms, SystemVerilog methodology, and self-checking testbenches. AMS verification has tended to be ad-hoc or sharply divided into separate analog… Read More

IC Implementation Tool Gets a Rewrite, Now 10X Faster

EDA start-up companies often have the advantage over established vendors by being able to start from scratch, instead of having to maintain some legacy code that no longer is competitive. But what happens when the established vendor decides to rewrite their IC implementation tools from scratch? In this case it’s good news,… Read More