SOC designers face choices when it comes to choosing how to implement algorithms in their designs. Moving them to hardware usually offers advantages of smaller area, less power and faster processing. Witness the migration of block chain hashing from CPUs to ASICs. However, these advantages can come with trade-offs. For one, hardware is fixed during the chip design and cannot be adapted and modified, possibly leaving an SOC with a less than optimal or potentially out of date algorithm.

The appeal of using processors to implement algorithms is undeniable. Code can be adapted for evolving specifications or standards. As technology advances SOCs can receive code updates that accommodate newer or improved methods of solving problems. However, this flexibility comes at the costs articulated above.

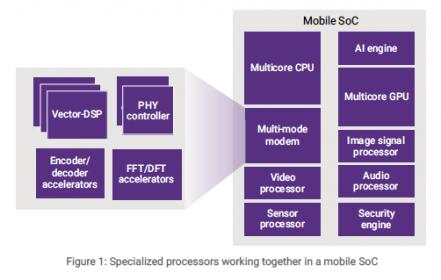

The development of special purpose processors has made this dilemma a little easier for SOC designers by providing many of the advantages of each approach in a single solution. There are many examples of these: GPUs, vision processors, network processors, neural network processors, FEC processors, etc. Indeed, most SOCs are built with a host of processors that contain optimizations for specific tasks. However, in the search for product differentiation, designers sometimes are looking for special purpose processors or accelerators that are not available. The features of these might include unique parallelization, special branching, pipelining, new data types, special instructions, etc.

If there is an advantage to be gained by adding a special purpose processor, the barriers to creating one and adding it to a design have been too high for most SOC teams. Synopsys has written a white paper that talks about how these barriers can be overcome, to yield improved design time and product performance.

Handcrafting a specialized processor and optimizing it for an SOC comes with a lot of overhead. In addition to customized software compilers and debuggers, RTL and simulation views are required. Importantly, it is necessary to iterate on processor design and its application code to ensure the system will work as intended and as efficiently as possible. This means looping in the code compiler and the RTL synthesis tool, having them work from an easily modified processor specification.

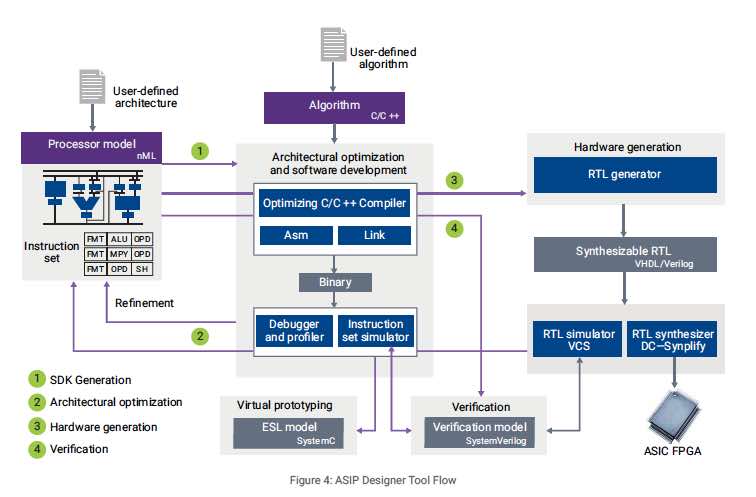

Synopsys solves this problem with their ASIP Designer. The process begins with their nML, a high-level language for specifying the architecture of the processor. nML is hierarchical and highly structured. It can be thought of as being similar to Verilog or VHDL, but is used for the specification of a processor and is used to create downstream deliverables.

The nML drives a retargetable SDK that consists of an optimized C/C++ compiler, assembler/disassembler, linker, cycle-accurate and bit accurate instruction set simulator and graphical debugger. Next the nML can be used to generate a hardware description of the processor in fully synthesizable RTL. The nML can be fully verified for correctness by the ASIP Designer. Subsequently, the RTL model produced can also be verified and checked to see that it implements the processor model correctly. Included in ASIP Designer, Synopsys provides extensive verification tools, along with debugging and diagnostic capabilities to run consistency checks, and produce reports on connectivity analysis, hardware conflicts, unused instructions, pipeline hazards and much more.

The Synopsys ASIP Designer opens up many opportunities to take advantage of the power and flexibility of special purpose processors. In a “best of both worlds” solution, highly optimized processors can be used as a middle ground between bulky general-purpose processors and hardwired RTL code. Specializations ideally suited to the task at hand can be easily implemented in any aspect of the custom processor. Best of all, a full featured SDK is ready from the moment of specification to validate performance of the architecture and accelerate firmware development.

The benefits of specialized processors cannot be overstated. They can be tuned and optimized to perform a wide range of options with very minimal overhead. General purpose processors are just that – general purpose. They are frequently not a good fit when the problem they are being applied to is narrow and well understood. Historically the problem has always been the high effort required to create new special purpose processors. With their ASIP Designer, Synopsys has taken many of its core strengths and applied them to solve a difficult problem. Their white paper on “Softening Hardware” is very informative and goes into greater detail on both the benefits of their solution and on the details of its implementation. It is a good read.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.