The state of Texas hosted two or our industry’s big technical conferences and trade shows this year: DAC and ITC (International Test Conference). IC designers know about DAC in Austin, and test engineers know about ITC in Dallas. I travelled to Austin to cover DAC this past summer, and I was able to connect with Robert Ruiz of Synopsys by phone last week to get the scoop on all things test. For some chips the costs for packaging and testing can rival that of silicon fabrication or design, so it’s important to know how to minimize time on the tester while maximizing test metrics like fault coverage.

The three big messages from Synopsys at ITC this year were:

- TetraMAX IIfor ATPG is in production use by real customers

- The automotive market has demanding quality requirements, so ISO 26262 certification is a big deal

- 7nm FinFETtechnology has some tricky, new faults

ATPG

Automatic Test Pattern Generation software has been around now for decades to create patterns with higher fault coverage than what can be achieved by functional vectors and manual efforts, however the size of chips has been growing by orders of magnitude. Back in July we first heard about the initial results of a re-written ATPG tool called TetraMAX II that were up to 10X faster while using up to 25% fewer patterns, so at ITC we heard more from real test customers like:

- Toshiba (50-90% fewer patterns, 2-13X faster)

- Broadcom (30-50% fewer patterns, 1.3-5X faster)

- STMicroelectronics (30-80% fewer patterns, 2-12X faster)

Related blog – EDA Tool for ATPG – Refactor or Rewrite?

Automotive

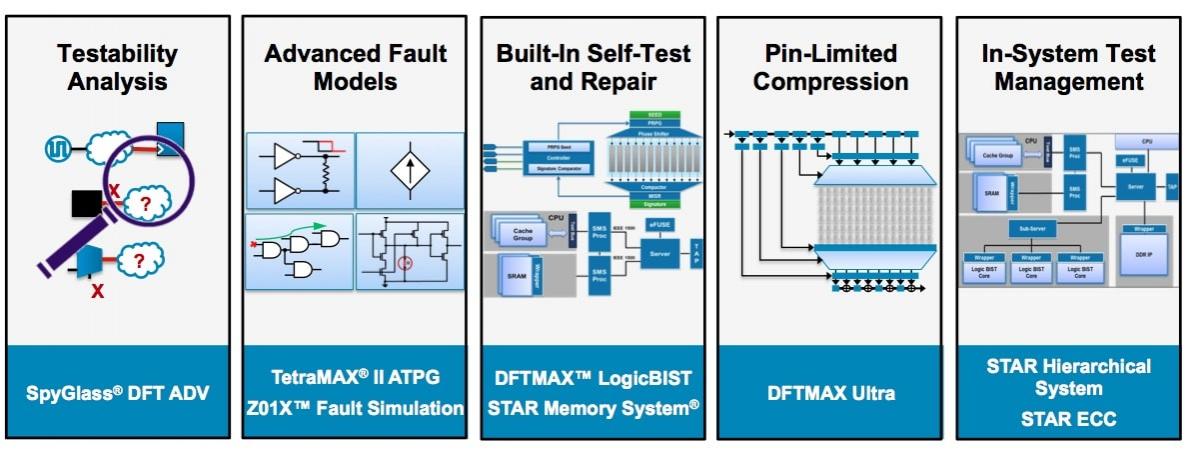

Our semiconductor industry sees real growth in the electronic content of traditional automobiles, ADAS and even driverless cars. To meet the rigorous demands of the ISO 26262 certification requires many test technologies, and Synopsys with the Atrenta acquisition has some unique testability analysis at the RTL level even before gate-level implementation. Five specific test tools have been certified for the ISO 26262 standard:

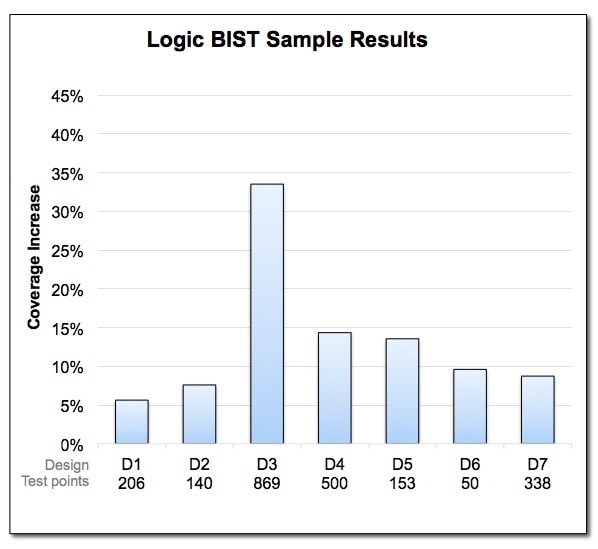

The test goals for chips used in automotive is to achieve a very low DPPM, have in-system monitoring, mitigate the effects of soft errors, and automate the BIST methodology. Adding test points is a well-known technique for improving observability or controllability, but now you need to automate this process by having a tool that accounts for the congestion of the P&R tool while continuing to meet timing paths. This approach is called physically-aware test points and by using SpyGlass DFT ADV and DFTMAX tools you can actually lower test costs. Here’s a chart showing the amount of fault coverage improvement by adding test points, and in the best case up to a 33% increase in coverage resulted:

Running a fault simulator is still a useful methodology to increase functional coverage, so Synopsys acquired the leading Z01X fault simulator from WinterLogic back in March 2016. Automotive chip designers use Z01X to reduce their DPPM levels even lower as it supports cell-aware faults. Using the Synopsys tools that are ISO 26262 certified helps get your IC certified, includes all documents required for certification, has tracking and notification on any safety issues, and is monitored by an automotive functional safety officer.

Hierarchy is a natural part of the SoC design process, so the DesignWare STAR Hierarchical System adds hierarchy support for testing, saving you time on the tester and even letting you monitor safety-critical metrics like clock frequency, duty cycle or even voltages over time. Example customers using Synopsys for their test approach are: Elmos Semiconductor, MegaChips, Micronas, Renesas Electronics and Toshiba.

7nm FinFET

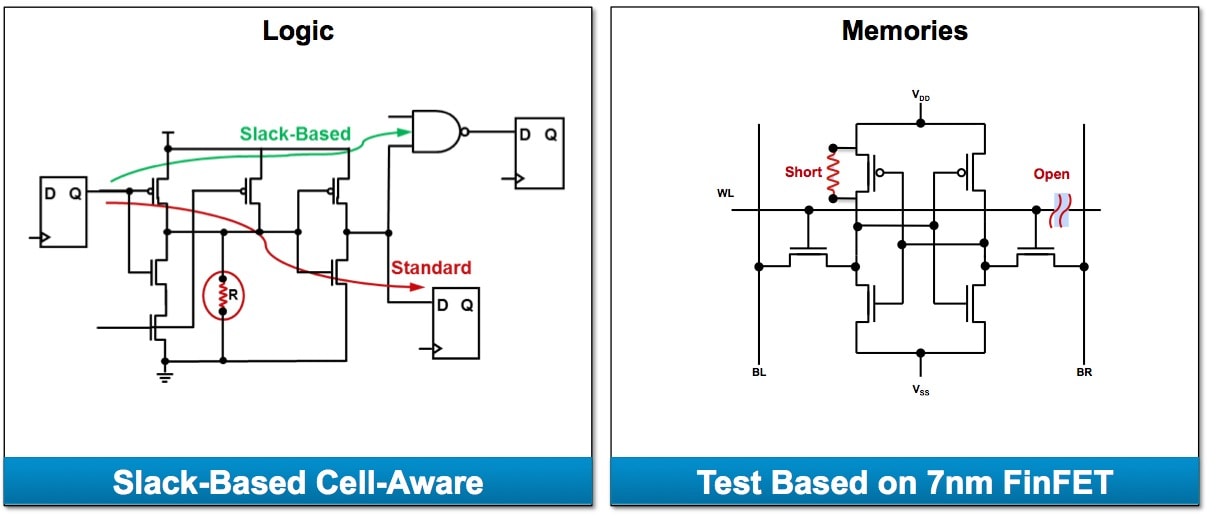

I’m just staring to read about 10nm silicon from foundries like Samsung, so it’s no surprise that the next generation of FinFET technology at 7nm is in the design phase now. IBM pioneered the concept of cell-aware fault modeling and now Synopsys extends that concept into something they call slack-based cell-aware fault modeling:

Synopsys has a long history in Static Timing Analysis (STA) which enables slack-based cell-aware testing. The semiconductor IP group at Synopsys is designing both logic and memory cells at 7nm, so they need to model and test for all of the subtle, new defects like shorts and opens inside of a memory cell. For test engineers one big benefit is on the diagnostic side where you can have the tool pinpoint where in the IC layout a certain type of fault is coming from, which really speeds up the time to find a physical cause for failure analysis purposes.

Related blog – Did my FPGA Just Fail?

As fabs and foundries ramp up a new process node they can use a tool called Yield Explorer for their data analysis and correlation across multiple dies and runs. Imagination Technologies is another Synopsys customer that is using the embedded memory test and repair approach for their latest chips.

Summary

ITC is always a big showcase to bring your test technology out and let the world know what your test approaches are, so in 2016 we see Synopsys continuing to prove their worth in the areas of a new ATPG tool, ISO 26262 certification for the automotive market and readiness for the next FinFET process at 7nm.

Related blog – Foundation IP for Automotive: so Stringent Quality Requirements!

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.