In the life of all EDA software tools comes that moment when new requirements make developers stop and ask, should I continue to refactor the existing code or just start all over from scratch using a new approach? Synopsys came to that junction point when ATPG run times were reaching days or even weeks on the largest IC designs, something that caused too much pain for SoC designers trying to meet their tapeout schedules and have ATPG vectors ready in time for first silicon samples coming back from the fab. Necessity is the mother of invention, so the engineers at Synopsys went about the epic task of rewriting their popular ATPG tool TetraMAX to meet several emerging test challenges:

- Increase in IC design size

- New, subtle defects

- FinFET technology

- Improving diagnostics

- Meeting automotive standards

- Utilizing multi-core workstations

- Efficient RAM usage

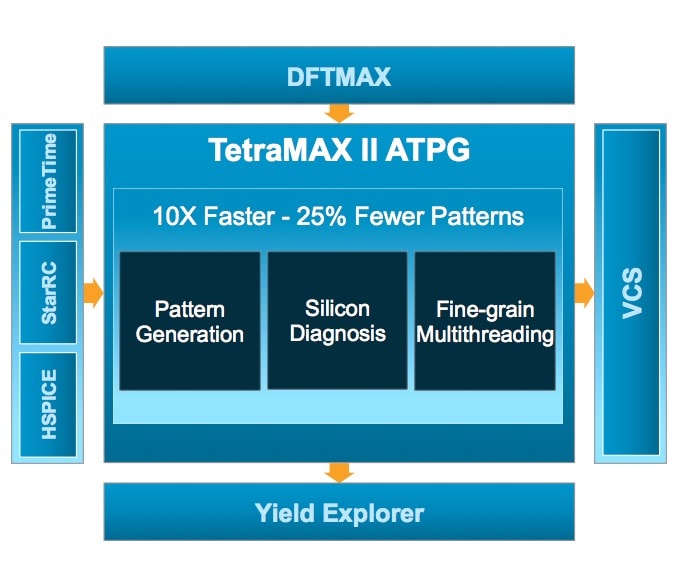

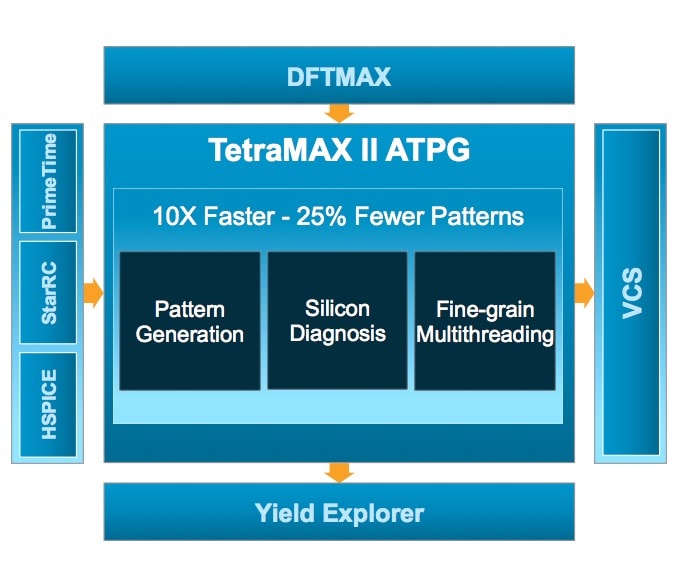

The new ATPG tool has a familiar name, TetraMAX II. We first started hearing about a new ATPG technology from Synopsys in the Fall of 2015, and now we learned that three major sections were re-written for:

- Pattern generation

- Silicon diagnostics

- Fine-grain multi-threading

So what did the rewrite accomplish? Plenty.

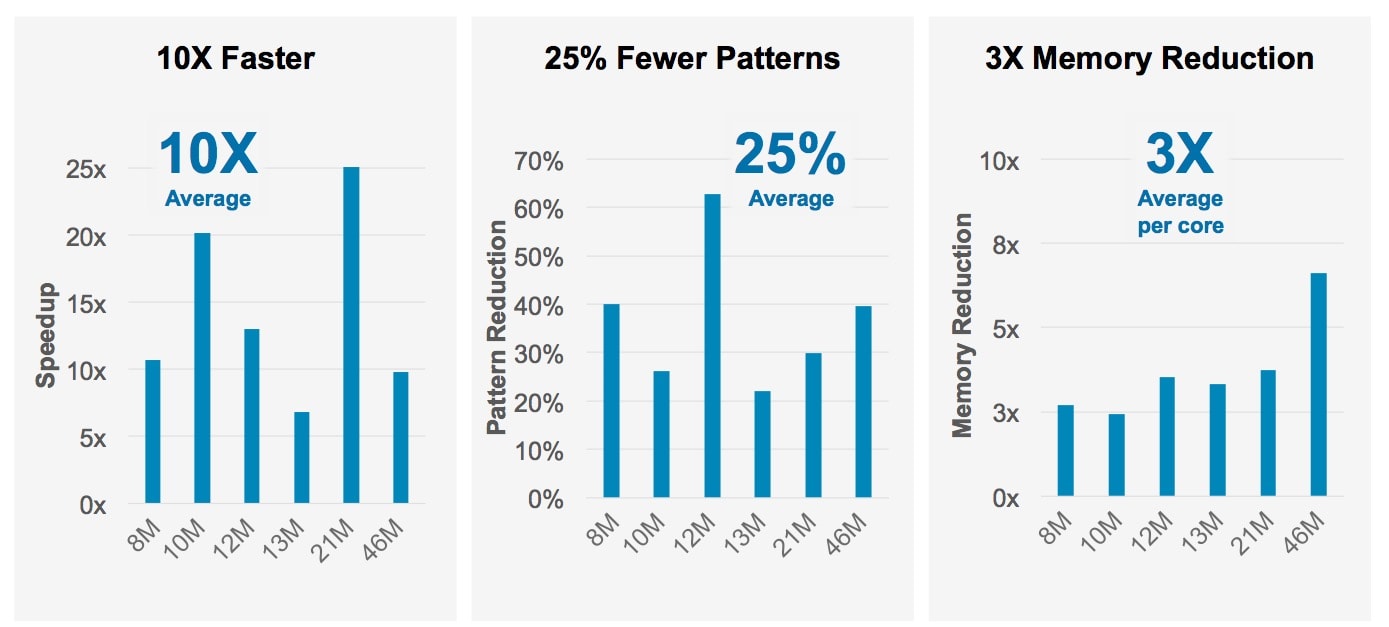

- 10X faster tester pattern generation

- 25% fewer patterns

- 3X reduction in RAM

- ISO 26262 certified for automotive safety

Here’s a quick comparison of TetraMAX II versus the original across several customer designs:

All of the inputs and outputs from TetraMAX II are the same as with the original TetraMAX, so I expect that the learning curve is going to be quite brief to existing ATPG users. Some old commands are now ignored with TetraMAX II, like the command to trade off run time versus patterns.

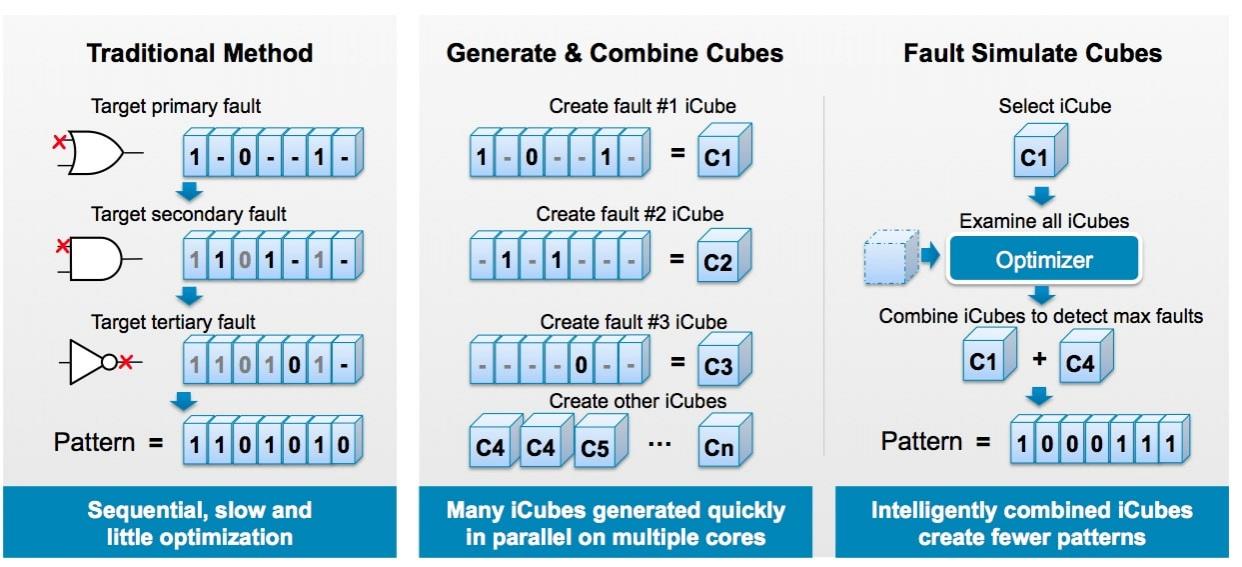

How does Synospys get fewer test patterns in this new ATPG tool? The traditional method of targeting faults in a gate-level netlist are sequential, slow and not really optimized. With TetraMAX II the fault targeting approach uses something called iCubes, where many iCubes can be generated quickly in parallel on multiple cores. Each iCube is examined to see how it can be combined with other iCubes to detect the maximum number of faults with the fewest patterns. This fault and pattern optimization is all “under the hood” and protected by patents.

ATPG users can now expect that generating patterns on large chip designs will no longer be a bottleneck, and that with more efficient patterns the tester time goes down saving costs, plus you can now fit your ATPG runs onto machines using RAM way more efficiently. Automotive industry designers will be glad to know that this new Synopsys tool has been certified by SGS-TUV Saar GmbH up to ASIL D requirements as part of the ISO 26262 qualification of the IC test process. Even the way that bugs are reported and fixed in this ATPG tool get tracked and notifications sent out for any safety-related issues, all monitored by a dedicated Synopsys automotive Functional Safety Officer.

So who is actually using TetraMAX II? So far I’ve heard that Toshiba used the tool and and found that the ATPG run times are shorter, plus they saw some 50% reduction in the number of test patterns. STMicroelectronics is talking about the 10X speed up in ATPG run times. Expect even more customer quotes over the next year as the installed base of TetraMAX users hears about the revamped TetraMAX II, does an evaluation, and eventually upgrades to get the new benefits.

Summary

Synopsys now offers a 2nd generation of ATPG tool dubbed TetraMAX II, and it runs some 10X faster, typically producing 25% fewer patterns, all while consuming 3X less RAM. Now the big question is price, so for that info you must follow up with the local Synopsys account team to get the details and also to start an evaluation.

Related Blogs

- SpyGlass DFT ADV accelerates test closure – Xilinx and Synopsys webinar

- Three New Things from ITC this year

Comments

There are no comments yet.

You must register or log in to view/post comments.