Last week at the #53DAC conference there was a lot of excitement in the air about custom IC design, especially at the luncheon that I attended on Tuesday from Synopsys where they had customers like STMicroelectronics, GSI Technology, Samsung Foundry and the Synopsys IP group talk about their experiences using the new Custom Compiler tool. The luncheon that they hosted was in the Hilton, and had the best food service at DAC this year, plus the room was packed with interested engineers.

STMicroelectronics

Atul Bhargava started out by explaining that his company helps make products for the smart city, smart home, smart driving and the IoT. Their primary technology is FDSOI and so they create their own libraries, foundation cells, I/O, memories and AMS designs. When they did a survey of their own IC designers it was discovered that their actual time was spent with 30% on transistor and cell placement, 25% in routing and 45% in validation (DRC, LVS, EM, IR drop, reliability).

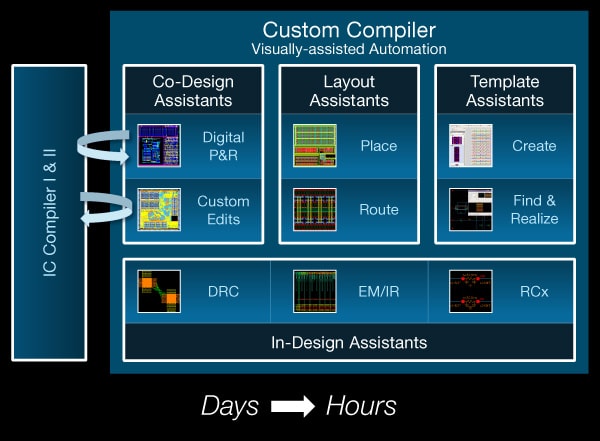

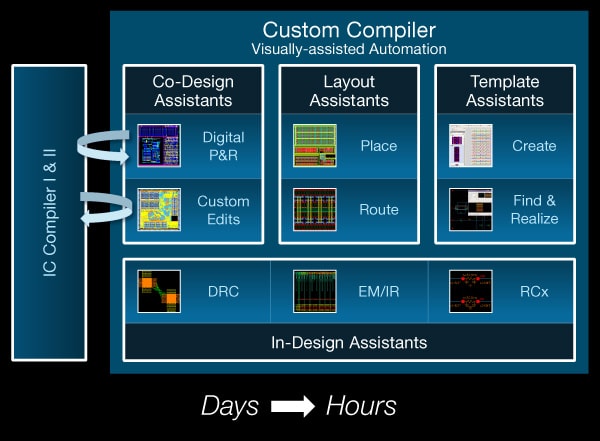

With the Customer Compiler tool they like using the symbolic editing in Custom Compiler, and how it helps automate digital layout devices. Analog designers can quickly place dummy devices and use common centroid topology automation. Even their analog layout patterns can be saved for future reuse. EM analysis is a quick process in Custom Compiler, even pushing it to an earlier part of the design flow right after schematic capture where they can start to plugin in currents for Peak, Average and RMS, then decide how many vias are required for a detailed layout.

The look and feel of Customer Compiler is very much like a modern web browser, so it’s intuitive and easy to learn.

This group has been able to take an iPDK from 28nm PDSOI and quickly migrate it, plus all of the required IP migrated. Even the SRAM and standard cell groups are now using Custom Compiler.

GSI Technology

Up second was Randy You, and his company was founded in 1995 with offices in both Sunnyvale and Taiwan, growing to 140 people now. Their IC designs are differentiated from competitors by offering higher performance and lower power consumption. On a recent 16nm project they started using the Custom Compiler tools and quickly noticed three areas of design challenge: design rule complexity, EM/IR analysis and balanced net routing.

With the Custom Compiler layout tool they use the Dynamic Rule Distance (DRD) feature to show layout designers if there are any design rule issues as they do custom layout, it even works with double patterning. A full DRC is still required after using the DRD feature, but using DRD reduces the number of full DRC runs required.

In their EM/IR design flow they can start with schematics, run circuit simulations to create currents, then the current values are used to quickly recommend metal widths required for layout, even before running a detailed EM/IR analysis, reducing layout/analysis iterations and saving time.

Balanced nets can now be auto-routed instead of manual routing, the clock tree can be auto routed to all I/O block.

Samsung Foundry

Next we heard from Bonhyuck Koo about their iPDK development group that does FinFET design, uses multi patterning, and combats design rule complexity. On their 14nm FinFET process the Customer Compiler tools were used in a color-aware design flow. They can even do density checks with coloring and have automated coloring.

For DRC and LVS checks they use an in-design approach, instead of solely relying on a batch approach which causes too many iterations to reach a clean layout. Doing early EM checks also enables designers to meet reliability requirements earlier in the tool flow, instead of waiting too late in the flow. The 10nm iPDK is coming next month in July, so stay tuned for the formal announcement.

Synopsys IP Group

Did you know that Synopsys has about 2,400 engineers doing soft IP design and 1,300 AMS IP designers? They use their own Custom Compiler tools for all of their work and have done test chips taped out for Samsung 14 LPE, 14LPP, TSMC 16FFP and others. Synopsys has been doing FinFET designs since 2012. Their custom IC challenges are: DRC complexity, EM/IR analysis, density, performance, coloring, segmentation, and the annoying fact that fin pitch doesn’t equal metal pitch.

Working with the foundries they get early PDK layout rules and start making their new cells with an eye towards allowing changes as the rules get updated. The EM assistant helps reduce iterations and closure for reliability concerns. A video comparison showed the same custom IC layout task with and without all of the Custom Compiler automation features, and the net result was a whopping 7X improvement.

Summary

Users have some real choices today when it comes to custom IC layout design tools, and Synopsys appears to have reached critical mass with their Customer Compiler tools. It’s worth taking a look at their new tools to see how they compare with your existing design flow productivity.

Comments

There are no comments yet.

You must register or log in to view/post comments.