Fed up with ECOing your way out of test problems? You might want to register for this webinar.When you’re building monster SoC FPGAs, you have all the same problems you have with any  other SoC. That includes getting to very high test coverage as quickly as you can with a design targeted to the most advanced processes. We’re not just talking the basic stuck-at coverage – that has to be very high. But you also have to have high at-speed coverage and, in these days of test compression, you have to fix areas of random pattern resistance which otherwise force longer test sequences and therefore longer test chains, undoing a lot of the advantages of compression.

other SoC. That includes getting to very high test coverage as quickly as you can with a design targeted to the most advanced processes. We’re not just talking the basic stuck-at coverage – that has to be very high. But you also have to have high at-speed coverage and, in these days of test compression, you have to fix areas of random pattern resistance which otherwise force longer test sequences and therefore longer test chains, undoing a lot of the advantages of compression.

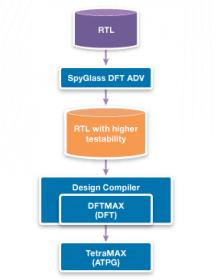

Even basic stuck-at testability problems can be challenging to find in large designs using IPs from multiple sources. Problems limiting at-speed testability and random pattern resistance are simply too hard to track down without automation. That’s where Synopsys SpyGlass™ DFT ADV comes in. This tool will find coverage problems of multiple types and will help you isolate root causes; you can fix these through logic changes or by adding testpoints.

I know something about this technology since I was CTO at Atrenta for 15 years. SpyGlass DFT has become a must-have in many design for test groups in some of the biggest semiconductor and systems companies in the industry.

Learn more about how Xilinx uses this technology on their biggest and baddest SoC FPGAs to save weeks of test problem ECOs . Save the date – April 28, 10am Pacific.

You can register for this event HERE.

Web event: Xilinx and Synopsys Present: Meeting Test Goals Faster with SpyGlass DFT ADV

Date: April 28, 2016

Time:10:00 AM PDT

Duration: 45 minutes

Early detection of testability issues can prevent major bottlenecks downstream and avoid time-consuming design iterations. In this webinar, Synopsys presents new techniques and capabilities available in SpyGlass DFT ADV such as high-impact test points to boost coverage, reduce the number of patterns, and minimize test costs. Our guest speaker from Xilinx discusses test challenges associated with large SoC designs such as the Xilinx Zynq UltraScale chip family, and illustrates how SpyGlass DFT ADV addresses testability issues early in the design flow, saving weeks of complex DFT-related ECOs.

Speakers:

Amitava Majumdar

Principal Engineer, Programmable Platforms Group, Xilinx, Inc.

Amitava (Amit) Majumdar is with the High Speed Products Division of Xilinx’ Programmable Platform Group, responsible for defining unified DFx methodologies for digital and mixed signal IPs across Xilinx’ SOC products. These methodologies include test, silicon and application debug, characterization, yield and error tolerance capabilities in the presence of security and safety and power management features. After a brief stint as an EE faculty member at SIU-C, prior to joining Xilinx, Amit moved into the industry, working on various DFx topics at Crosscheck, Apple, Viewlogic, Synopsys, SUN Microsystems, Stratosphere Solutions and AMD. Amit has worked on 50+ successful tape-outs in various roles, ranging from front-end design to post silicon work as an engineer and manager. He has a wide range of interests, from statistical circuit design to data-compression, machine learning and other multi-dimensional optimization problems. Amit received a BE-Hons degree in Electrical and Electronics Engineering from BITS, Pilani, an MS degree in Electrical and Computer Engineering from UMASS, Amherst and a PhD in Electrical Engineering from USC.

Anthony Joseph

Applications Engineer, Synopsys

Anthony “Al” Joseph has over 30 years of experience in ASIC design and verification – the most recent 15 years focused on the SpyGlass RTL signoff platform. Anthony currently is a Senior CAE for the SpyGlass DFT ADV product family at Synopsys.

Dmitry Melnik

Marketing Manager, Synopsys

Dmitry Melnik is a Product Marketing Manager in Synopsys’ RTL Synthesis and Test group. He has more than 10 years of combined experience in EDA R&D, field applications and product management. He holds an MS degree in Computer Systems Engineering from KNURE, Ukraine.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.