Synopsys hosted a lunch session on Thursday of DVCon. Michael Sanie of Synopsys opened the session,  with a look back at the last DVCon where he had talked about Verification Compiler (VC) and extending the platform to Verification Continuum, which adds emulation and FPGA-based prototyping (HAPS – there was a very cool HAPS demo in the Expo Hall).

with a look back at the last DVCon where he had talked about Verification Compiler (VC) and extending the platform to Verification Continuum, which adds emulation and FPGA-based prototyping (HAPS – there was a very cool HAPS demo in the Expo Hall).

Verification Compiler and Continuum

Michael gave a high-level update on Synopsys verification:

· Great momentum behind VC Formal – including a native integration with simulation and coverage analysis to drive root-cause analysis of problems detected in simulation

· Lots of native integrations (some examples were Unified compile flow for simulation and debug)and Integration of the Siloti technology for smaller debug databases

· The VC apps library has grown beyond 300 entries (they stopped counting after 300)

On SpyGlass integration, sounds like the plan is to infuse key SpyGlass capabilities into VC and key VC capabilities into SpyGlass, which seems a reasonable low-disruption approach to keep everyone happy. For example, the SpyGlass Verdi plugin combines the Verdi hierarchy tree, HDL navigation and waveform viewer with SpyGlass messages, shell and incremental schematic.

He wrapped up with a mention of some of the work they are doing for Automotive design and their recent acquisition of WinterLogic, which will be key to functional safety verification and ISO 26262 compliance testing.

Verdi Update

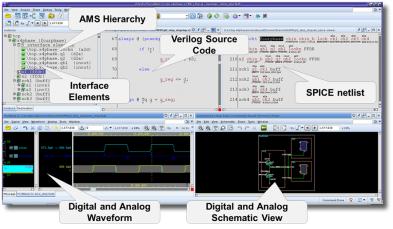

Vaishnav Gorur (Synopsys verification product marketing) gave an update on Verdi. Their most recent innovation is AMS debug, a pretty cool way to visualize together digital and analog waveforms along with corresponding RTL and Spice netlists. Other very nice features include:

· Reverse debug – debug backwards in time from whatever point you stopped/paused. You can even reverse step in debug

· An integrated protocol and memory protocol analyzer

· A performance analyzer, where you can set thresholds to trigger debug around violating transactions

· Integrated coverage management, linked to your verification / coverage plan

· Accelerating power analysis leveraging the Siloti correlation technology (mapping RTL to gate simulations) and PT-PX

NVIDIA experience with VC Formal and simulation

Syed Suhaib, who is the formal verification project manager at NVIDIA, presented his experiences in combining the best of formal and simulation to get to verification closure. He started by saying that manual effort still dominates verification closure for reachability testing in cases which seem resistant to coverage.

Especially at the tail-end of the project when schedules are tight, the last few coverage cases are hard to close, many because they are unreachable. These can be analyzed using formal techniques to assess if cases are truly unreachable (in which case you can define an exclusion) or to get hints on how to reach those cases.

But setting up formal proofs case-by-case is very tedious, error-prone and impractical. A much better way starts with formal proof natively integrated with simulation. Proofs can be triggered in parallel runs from those last few cases. NVIDIA collaborated with Synopsys on development of this flow and estimated it has saved them 2000 engineering hours on their last project.

To learn more about Verdi and especially Verdi-AMS, click HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.