As SoC and IP designs continue to increase in complexity while schedules accelerate, verification teams are looking for methodologies to improve design confidence more quickly. Formal verification techniques provide one route to improved design confidence, and the increase in papers and interest at industry conferences… Read More

Tag: vc formal

An InFormal Chat

Any sufficiently advanced technology is indistinguishable from magic, as the saying goes. Which is all very well when the purpose is entertainment or serving the arcane skills of a select priesthood, but it’s not a good way to grow a market. Then you want to dispel the magic aura, make the basic mechanics more accessible to a wider… Read More

Quantifying Formal Coverage

Verification coverage is a tricky concept. Ideally a definition would measure against how many paths were tested of every possible path through the complete state graph, but that goal is unimaginably out of reach for any typical design. Instead we fall back on proxies for completeness, like hitting every line in the code. This … Read More

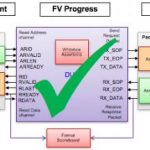

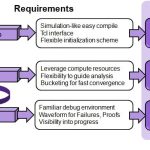

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

Verdi Update and NVIDIA on Verification Compiler

Synopsys hosted a lunch session on Thursday of DVCon. Michael Sanie of Synopsys opened the session, with a look back at the last DVCon where he had talked about Verification Compiler (VC) and extending the platform to Verification Continuum, which adds emulation and FPGA-based prototyping (HAPS – there was a very cool HAPS demo… Read More