We said this in the past, but let’s reiterate that IoT devices will be successful if they can meet low-cost and low-power requirements. Low-cost is the condition for IoT devices market penetration, I mean such a market adoption that we count several IoT systems (and dozens of devices) in every house. That’s the only way to reach the forecast predicting 20 billion of devices by 2020 and the condition translate into an IoT edge device cost below $10, not above $100 as we can see it today. The low power condition also obliges to completely rethink the device architecture and optimize the various existing IP implementation to create more efficient sub-system IP.

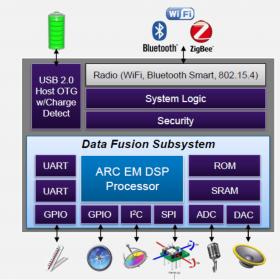

The move from single sensor application to voice and multiple sensors, known as sensor fusion, requires higher levels of signal processing, driving higher DSP performances. Moreover, user interface developments also require higher levels of signal processing. At the same time users are demanding more complex features, they expect devices with longer battery life. Battery operating for only a few days used to be OK in the past, but users expect now an IoT device to stay active two weeks between charging. That’s why Synopsys has completely re-architecture their Data Fusion Subsystem (pictured below). Such IoT SoC or Microcontroller should be powered with AA/coin or Lithium battery, support Bluetooth, 802.15.4, Zigbee or WiFi wireless connectivity. Technology and IP needs can be complex as the SoC may have to embark NVM (Flash or MTP), support various interfaces and provide high level of security. If the design can target 180 or 90nm to validate the IoT concept, high production level will require moving to 65, 55 or 40nm technology node.

Synopsys launches DesignWare Smart Data Fusion IP Subsystem integrating latest ARC EM9D and EM11D processors for highly-efficient DSP performance. This subsystem integrates a microDMA controller providing 4x faster access times, smart enough to decrease system-level energy consumption by enabling data transfers during processor sleep modes. Just take a look at data processing analysis:

- EM core is in sleep for data collection

- EM core and AHB Bus are inactive during data storage

- Data access is 4x faster for processing

- Overall sensor data processing exhibit a much lower power compared with a typical system accessing memory and DMA over the Bus.

Implementing hardware accelerators like Fast Math functions or a crypto pack (AES/SHA/3DES), tightly coupled memory and peripherals allow reducing power consumption by up to 85 percent compared to discrete solutions. ARC EM DSP cores have been designed for ultra low-power control and DSP efficiency, thanks to an energy-efficient 3-stages RISC pipeline, unified single cycle 32×32 MUL/MAC unit and dedicated, energy efficient signal processing of voice/speech, audio and sensor data. Synopsys has implemented XY memory to increase DSP performance and provide software drivers and an extensive library of DSP functions such as FFT and DCT, FIR and IIR filters to speed application software development.

Synopsys can propose a demo platform developed in collaboration with Renesas, including MonArch MCU running @ 200 MHz, 3 megapixel camera for image/gesture and Bluetooth supporting wireless audio output and run-time communication to tablet. The platform supports MP3 playback and SD card for audio storage.

Several applications can be demonstrated, like voice activation & control using Sensory’s TrulyHandsfree S/W, 9D positioning & activation based on Hillcrest Labs’MotionEngine S/W and Face detection and gesture control interface using Synopsys proprietary demonstration code.

Availability

The DesignWare Smart Data Fusion IP Subsystem will be available in February 2016.

Learn more about the Smart Data Fusion IP Subsystem: https://www.synopsys.com/dw/ipdir.php?ds=smart-data-fusion-subsystem

From Eric Esteve from IPNEST

Share this post via:

Comments

0 Replies to “Does IoT need Sensor Fusion? Yes, but at low-power, low cost…and higher performance”

You must register or log in to view/post comments.