A maturetool. A legacytool. A tool that’s a little long in the tooth. We have all used these terms to refer to an EDA product that has not been able to keep up with technical challenges of model complexity, performance, or new features required by current SoC and system design requirements.

With the process development trend of Moore’s Law and the transition to FinFET technologies, tools for circuit simulation and analysis are especially susceptible. Perhaps the underlying algorithms in the code are inherently single-threaded, and do not scale to current multi-core processors and/or distributed execution. The data model used may not readily support optimization of complex networks (e.g., ones with lots of small parasitic elements) into more efficient, reduced formulations. Convergence of the network solution (at DC or at simulation timesteps) may by problematic, impacting performance. Or, perhaps the output results and reports do not include the requisite utilities and scripting support to allow designers to quickly data mine the parameters of interest.

Thankfully, these “legacy” issues definitely do not apply to HSPICE, which recently celebrated its 35th anniversary.

At the recent HSPICE SIG users group meeting (and birthday party :D), Synopsys emcee Brian Chen asked the audience if anyone knew of another EDA product that was going strong at 35. We couldn’t think of one.

The HSPICE user and Synopsys presentations at the SIG meeting were especially enlightening. Cisco, Qualcomm, Altera and Xilinx presented unique analysis problems and network modeling requirements, and how they leveraged HSPICE features to find solutions. The presenters were mobbed at the end of the evening by members of the audience, interested in more details. I couldn’t help but think that there are undoubtedly a multitude of HSPICE capabilities beyond “traditional” circuit simulation which many users, myself included, are likely not aware. (More on some key features shortly.)

The Synopsys update from Scott Wedge, HSPICE R&D, made it clear why the tool has continued to remain the gold standard, avoiding the mature tool pitfalls mentioned above.

Scott started by emphasizing the investment that Synopsys makes in user support, with direct feedback to the R&D team. All EDA vendors certainly utilize customer input to guide new feature development and prioritization, but the examples Scott provided really drove home the importance given to this feedback by the HSPICE development team.

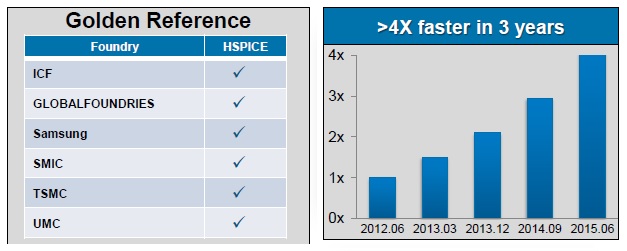

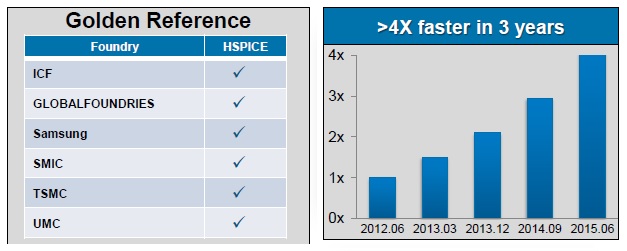

Then, Scott emphasized how the HSPICE team has focused on improving tool performance and addressing model complexity:

- 4X performance improvement in 3 years

- improved parallel efficiency of network solver algorithms (both Linux and Windows versions)

- unique optimization of DC convergence in FinFET circuits, and optimization of networks with many (small) parasitics relative to devices

(If you’ve worked with extracted FinFET circuits, you are no doubt seeing many more extracted parasitics, as well as the unique issues related to convergence with dummy gate devices.)

- emphasis on qualification of BSIM models with all foundries (including new FinFET self-heating and device aging mechanisms)

- new closed loop stability analysis (phase margin, gain margin) features

- transient simulation noise power/spectral density measurement enhancements

The SIG vendor presentations spanned the domains of advanced modeling, SerDes simulation, and efficient simulation regression analysis.

Cisco and Xilinx highlighted the need to enhance library component models to enable much greater accuracy. For example, a “simple” element such as a decoupling cap may need a more exact representation than a C value with an equivalent series resistance and inductance (ESR, ESL). HSPICE users are providing their own voltage-dependent, temperature-dependent, and frequency-dependent models, to enable more accurate impedance analysis for the most demanding, high-performance switching applications.

As the presentation from Altera emphasized, a simulation tool such as HSPICE needs a correspondingly rich waveform viewing and reporting environment, such as Custom WaveView, to enable data mining of results — e.g., scatterplots of measurements versus device parameters and variables, .meas versus .meas data correlation plotting, statistical calculations (mean, sigma).

A technical area where the HSPICE R&D team has clearly made significant investment is in support of SerDes analysis. Both the Qualcomm and Synopsys presentations highlighted the support for the requirements of serial link design that are incorporated into HSPICE, including:

- scattering parameter (S-parameter) based model utilities (SPUTILS): supports model reduction, passivity/causality analysis, etc. of an S-parameter Touchstone model

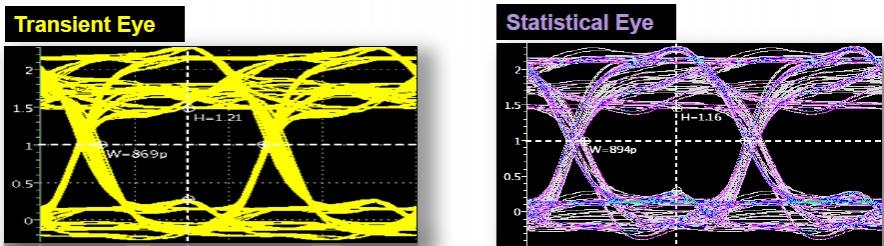

- Statistical Eye analysis (StatEye): Statistical Bit Error Rate (BER) analysis for a multi-port system, with injected jitter

An accurate transient analysis is used to calculate the impulse response of a number of small bit patterns, then statistical methods quickly generate the eye diagram as a probability density function (PDF) map that takes all the possible bit patterns into account.

Increasingly, single-ended high-speed links will no longer be accurately represented as Linear Time-Invariant (LTI) systems, due to increasingly non-linear drivers and rise/fall asymmetries in signaling levels, resulting in greater Inter-Symbol Interference (ISI). Traditionally, the superposition of the response to simple bit transition patterns is used for statistical characterization of an LTI system — while still applicable to the symmetry of differential signaling, that will no longer be sufficient for advanced single-ended interfaces. (Think LPDDR4.) HSPICE StatEye includes “multi-edge” pattern simulation and superposition to characterize the channel, maintaining the required accuracy for non-LTI statistical BER analysis.

- Transient Eye analysis (TranEye)

Using the results from the fast, statistical analysis of StatEye, HSPICE captures the bit patterns which cause the inner-most (worst-case) eye window. Using a derived pattern in subsequent transient analysis, designers can really delve into the causes of eye closure. Additionally, HSPICE can extract a time domain waveform at particular bit positions, which is extremely useful for adaptive equalization signal design.

It is clear that Synopsys is committed to investing in HSPICE performance optimization and feature development. It will be very interesting to see what the next 35 years brings.

More information on HSPICE is available at www.hspice.com.

-chipguy

Share this post via:

Comments

0 Replies to “HSPICE – 35 and looking good!”

You must register or log in to view/post comments.