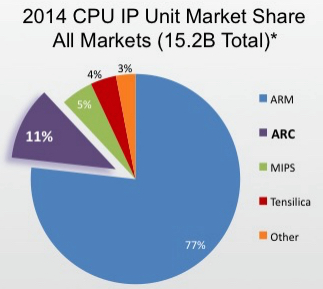

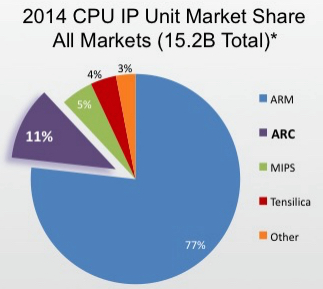

One of the big surprises I got at Synopsys’ ARC conference is that ARC is #2 in terms of share of licensed microprocessor shipments. I think most readers of Semiwiki would know ARM is #1 but would guess that MIPS (now owned by Imagination Technologies) is #2. But you’d be wrong, ARC is over twice as big.

One of the big surprises I got at Synopsys’ ARC conference is that ARC is #2 in terms of share of licensed microprocessor shipments. I think most readers of Semiwiki would know ARM is #1 but would guess that MIPS (now owned by Imagination Technologies) is #2. But you’d be wrong, ARC is over twice as big.

Last week Synopsys held the ARC Processor Summit. The first keynote was by Aart, who I guess I should describe officially as one of Synopsys’ two Co-CEOs. His presentation was titled IoT: From Silicon to Software which is the tagline that Synopsys has adopted as the acquisition of Coverity (and other companies) has put them firmly in the software space as well as the EDA and IP spaces. Aart said that in semiconductor there have really been just a few big waves. First the PC wave of computation. Next the mobility wave when mobile phones first came on the scene. The third wave was the combination of mobility and computation which gave us smartphones, and the next wave is IoT, which is really “smart everything.”

The second keynote was from Linley Gwenapp about the licensed microprocessor market. His forecast is for a CAGR of 13% through 2018, faster than the overall IP (or EDA) market. In 2014 there were 15.3B chips shipped containing one or more licensed microprocessor cores. The share broke out like this:

[TABLE] style=”width: 300px”

|-

| Company

| 2014 share

|-

| ARM

| 72%

|-

| Synopsys ARC

| 10.6%

|-

| Imagination MIPS

| 4.7%

|-

| Cadence Xtensa (Tensilica)

| 3.9%

|-

| Cortus

| 1.4%

|-

| Andes

| 1.2%

|-

| Other

| 0.2%

|-

Linley pointed out that process technology means that there is no longer a free lunch for raising transistor budgets. The Apple’s and Qualcomm’s of the world are pushing down to 14/16nm and on to 10nm. Lots of others are holding back at 28nm for the sweet spot of price/xtor. There is growth in cores going on with the number of cores per chip going from 2.9 in 2014 to a forecast of 4.6 in 2019. ARM owns the application processor main socket (where the architecture is visible to the apps programmers) but there are lots of other sockets up for grabs. Integration reduces the number of chips but not the number of cores. Indeed, many “peripherals” such as SERDES or Bluetooth also contain a microprocessor core. There is a trend for the top biggest suppliers to do more of their own IP although, in all cases, stlll licensing the main application processor architecture from ARM:

Linley pointed out that process technology means that there is no longer a free lunch for raising transistor budgets. The Apple’s and Qualcomm’s of the world are pushing down to 14/16nm and on to 10nm. Lots of others are holding back at 28nm for the sweet spot of price/xtor. There is growth in cores going on with the number of cores per chip going from 2.9 in 2014 to a forecast of 4.6 in 2019. ARM owns the application processor main socket (where the architecture is visible to the apps programmers) but there are lots of other sockets up for grabs. Integration reduces the number of chips but not the number of cores. Indeed, many “peripherals” such as SERDES or Bluetooth also contain a microprocessor core. There is a trend for the top biggest suppliers to do more of their own IP although, in all cases, stlll licensing the main application processor architecture from ARM:

[TABLE] class=”cms_table_grid” style=”width: 500px”

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | All Standard

| class=”cms_table_grid_td” | One Key IP in-house

| class=”cms_table_grid_td” | Almost all IP in-house

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Mediatek

Spreadtrum

Marvell

AllWinner

Rockchip

| class=”cms_table_grid_td” | Apple

Huawei (HiSilicon)

Samsung

| class=”cms_table_grid_td” | Qualcomm

Intel

Nvidia

|-

After the keynotes I sat down with John Koeter (who I interviewed just a few weeks ago) and Mike Thompson, who is the marketing guy for ARC processors and subsystems.

Synopsys acquired ARC through the Virage Logic acquistion 5 years ago. I can honestly say I expected Synopsys to largely ignore it and let it die on the vine, and focus their attention on partnering with ARM. But they did not. This made for a rocky relationship with ARM at first since they clearly both need each other for the high end (where ARC doesn’t have an offering) and their most leading edge customers in the most leading edge processes. Since acquiring the ARC business, Synopsys have tripled its size. They now have around 250 people working on ARC. They reckon the TAM for the low and medium end microprocessor cores is $400M so there is lots of room for growth.

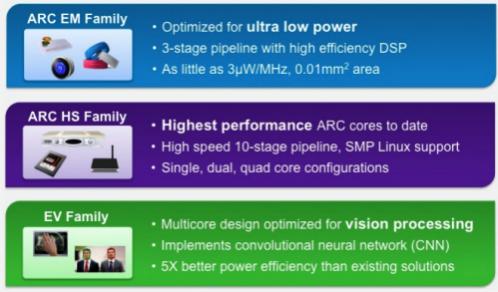

They gave me the big picture view of their product line. There are 4 lines:

- the low end EM cores compete with ARM’s Cortex M line (and cores from other vendors). There are 7 cores. Three-stage pipeline, no cache. The lowest end of all is the 650LE which is a fixed core but doesn’t require a per unit royalty

- the mid-range HS family HS34, HS36, HS38 for high performance embedded (with capability to add instructions)

- subsystems for embedded vision (one out now, a second in development for ADAS) which contain 2-4 HS cores and special object detection (convolutional neural networks CNN)

- roll-your-own-processor with tools to create a custom ASIP (application specific instruction processor) based on the Target compiler technology and the CoWare Processor Designer (both acquired a few years ago)

Since acquiring ARC they have upgraded the instruction set from v1 to v2 (added instructions, increased code density). The cores are very popular in storage and high-end networking. Broadcom’s home entertainment division has standardized on ARC. Currently Synopsys estimate they ship 1.7B units per year containing ARC cores, with perhaps 2.5-3 cores per chip, perhaps 4B cores per year. Another interesting statistic: about 90% of their customers write their own instructions and so customize the core to their own needs.

See also John Koeter: How To Be #1 in Interface IP

The ARC Processor page on the Synopsys website is here.

Comments

0 Replies to “We’re Number Two, We Try Harder”

You must register or log in to view/post comments.