Last week I sat down and talked to Bijan Kiani of Synopsys. He has marketing responsibility for design implementation products at Synopsys spanning digital, custom and analog mixed signal (AMS).

Last week I sat down and talked to Bijan Kiani of Synopsys. He has marketing responsibility for design implementation products at Synopsys spanning digital, custom and analog mixed signal (AMS).

He was born in Iran and after high school he moved to the UK. He got his PhD degree from University of Edinburgh. It turns out that I was doing my PhD at the same time although I don’t think we ever met. He was in EE and I was in CS and despite being literally across the road, in those days the departments had little to do with each other. He then worked for Burroughs and NEC in Scotland and joined European Silicon Structures (ES2) very early on. In another coincidence I also had a job offer from ES2 but in the end I decided to stay in the US at VLSI Technology. After ES2 didn’t really go anywhere he started his own company, InCA, doing ASIC emulation and prototyping. It was acquired by Zycad.

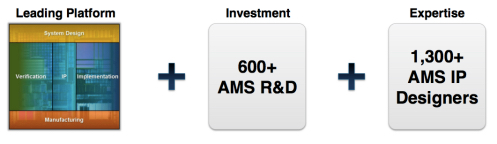

In 1996, so nearly 20 years ago, he joined Synopsys where he held various marketing roles. Now he has marketing responsibility for the entire digital and custom implementation products. On the custom side the heart of the portfolio is the Laker product that Synopsys acquired with SpringSoft and Custom Designer being developed organically. It turns out that Laker inside Synopsys has a different dynamic in the marketplace from when it was in SpringSoft. Before the acquisition I remember talking to SpringSoft, who bemoaned the fact that it was so hard to get foundries to create PDKs in a timely manner. But Synopsys is #1 in interface IP and foundries need that IP to be supported on their leading edge processes before fabless companies can tape out designs. This puts IP on the critical path to volume ramp in the foundries for leading edge processes. Since Synopsys uses their own custom layout solution for developing the IP, they need early collaboration with foundries to enhance custom tools and develop the PDKs before they can even start. By establishing close collaboration with leading foundries they have full support of the latest technologies.

In 1996, so nearly 20 years ago, he joined Synopsys where he held various marketing roles. Now he has marketing responsibility for the entire digital and custom implementation products. On the custom side the heart of the portfolio is the Laker product that Synopsys acquired with SpringSoft and Custom Designer being developed organically. It turns out that Laker inside Synopsys has a different dynamic in the marketplace from when it was in SpringSoft. Before the acquisition I remember talking to SpringSoft, who bemoaned the fact that it was so hard to get foundries to create PDKs in a timely manner. But Synopsys is #1 in interface IP and foundries need that IP to be supported on their leading edge processes before fabless companies can tape out designs. This puts IP on the critical path to volume ramp in the foundries for leading edge processes. Since Synopsys uses their own custom layout solution for developing the IP, they need early collaboration with foundries to enhance custom tools and develop the PDKs before they can even start. By establishing close collaboration with leading foundries they have full support of the latest technologies.

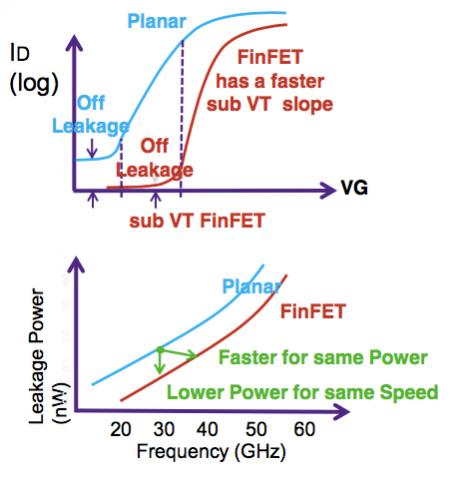

I asked Bijan why people would switch to the Synopsys solution. He said that as people move to FinFET, productivity for physical design takes a big hit because there is more to be done and checked. The complexity of new rules, restrictions such as fin placement, higher parasitics, metal track requirements and the high impact of physical effects all impact designer productivity. Using traditional custom design, productivity is reduced substantially, causing companies to take a fresh look for alternatives. Working with both the IP design centers which are active at the latest process nodes, as well as several leading customers who are the early adopters on these nodes Synopsys have developed many unique technologies that enhance basic layout editing. So they’re integrating a lot of great technologies that they have acquired such as Galaxy custom router and Helix placer to provide an assisted automation solution. Today they have very large logos that are using the Synopsys’ custom layout for FinFET or established nodes, including 5 of the top 20 fabless semiconductor companies.

I asked Bijan why people would switch to the Synopsys solution. He said that as people move to FinFET, productivity for physical design takes a big hit because there is more to be done and checked. The complexity of new rules, restrictions such as fin placement, higher parasitics, metal track requirements and the high impact of physical effects all impact designer productivity. Using traditional custom design, productivity is reduced substantially, causing companies to take a fresh look for alternatives. Working with both the IP design centers which are active at the latest process nodes, as well as several leading customers who are the early adopters on these nodes Synopsys have developed many unique technologies that enhance basic layout editing. So they’re integrating a lot of great technologies that they have acquired such as Galaxy custom router and Helix placer to provide an assisted automation solution. Today they have very large logos that are using the Synopsys’ custom layout for FinFET or established nodes, including 5 of the top 20 fabless semiconductor companies.

Synopsys is continuing to invest heavily to bring more automation to the market. The solution is complemented with strong tools for parasitic extraction, StarRC, and physical verification, IC Validator. Users love the integration of verification with layout so that design rule violations are flagged interactively as they work. With the complexity of design rules in modern process nodes, creating and then having to fix lots of obscure violations is part of life.

Of course Synopsys has a historically strong position in circuit simulation with the various simulators it has acquired or developed over the years: HSPICE, CustomSim and FineSim. One impressive statistic Bijan told me is that all leading Flash and DRAM memory chips are being verified with CustomSim and FineSim.

Another area of strength is that designs can be moved from custom layout into ICC and back, without losing any information (as opposed to using GDSII as the transfer format). So a block can be handled automatically in ICC, then moved for custom editing or shape-based routing for critical high-speed nets in the layout editor before being moved back into ICC for further integration. As Bijan emphasized, the strongest interest in the custom solution is in advanced processes, due to the productivity hit that customer are experiencing when moving from established nodes. But a lot of custom and AMS design is done in non-leading edge processes, 65nm or 130nm. The problems are simpler there than in the leading edge processes but Bijan emphasized that the automation technologies being developed for advanced node also can significantly help improve productivity in the established nodes. Strategically Synopsys has decided to build their beach-head in the most advanced processes where their automation, integration with ICC and their IP family all play a strong role.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.