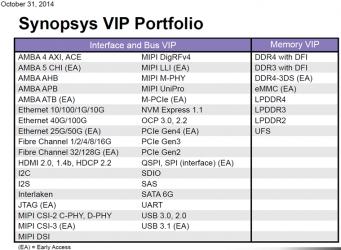

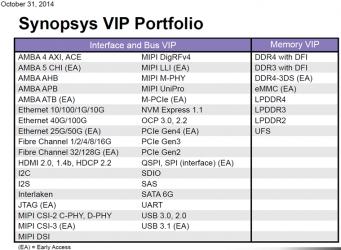

It’s likely that most of the current Semiwiki readers didn’t read this article posted in 2011, comparing Cadence and Synopsys with the Soviet Union and the USA, sharing the world in 1944 during the Yalta Conference. I was explaining in my post that Synopsys’s strong influence was on Design IP when Cadence’s preferred domain was on Verification IP. A kind of “Yalta effect” applied to the electronic design area (not to world regions!). If you missed this article, don’t worry as the content is no more relevant! Synopsys is still dominant in the IP business when excluding the large processor IP core segment (with $342 million revenues in 2013), but the company is also massively investing the VIP business, as we can see on the table below. To be fair, I must say that Cadence is also playing in Synopsys’s garden, investing in the Design IP business. But let’s take a look at the latest VIP news:

At first we can notice that Synopsys has developed this VIP port-folio around protocol based, Bus functions, like AMBA, OCP, I2C or I2S, and interfaces, starting with Ethernet, Fibre Channel or Interlaken supporting networking, then almost all the popular interfaces like seven MIPI specifications, PCI Express (including NVM Express and M-PCIe), SATA and USB. If you think that it’s easier to develop test suites to support protocol based function, you should take a look at the PCIe Gen4 specification document, a 1,000 pages book! This VIP port-folio probably represents several 100’s of man-year effort. Synopsys is claiming that these VIP have not only been used to verify Synopsys DesignWare Design IP, but also Synopsys’s customers and 3[SUP]rd[/SUP] party IP. These VIP can be exercised to verify customer design at SoC level, when the IP is embedded into an IC.

The memory VIP list is impressive as well as it cover from LPDDR2 to LPDDR4, UFS (a MIPI joined specification with JEDEC), eMMC, DDR3 and DDR4 both with DFI (the memory controller interface with the PHY) and DDR4-3DS.

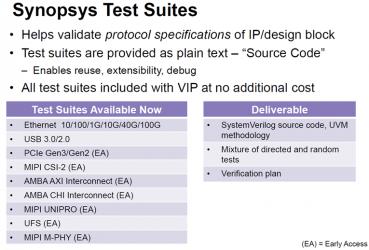

When dealing with VIP, the question about which language being used to develop it quickly surface. These VIP are native 100% SystemVerilog, offering native debug with Verdi and a fast turnaround time for simulations using any popular simulator. Because the test suites are delivered in source code, the design team can accelerate compliance verification and, even more important, be able to use the same source for all SoC, subsystem and IP verification needs.

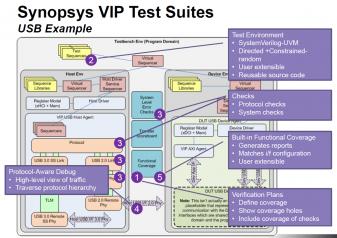

Now you should mobilize 100% of your remaining energy available in 2014 and take a look at the above picture. The slide is quite complex, but includes all pieces of information about Synopsys VIP strategy. I recommend starting from the bottom right to identify the USB device IP Device Under Test (DUT). The large grey box (still on the right side) represents the Device environment, and the USB device IP is accessible through a VIP AXI Agent. If you move to the left side of the picture, you will notice the VIP Agent, a VIP USB Host. Just remember that a VIP is to an IP that a glove is to a hand: is you verify a USB Device IP, you will use a USB Host VIP. From this point of view, VIP is just like Design IP. The difference between VIP and IP comes with Test Suites (included into the purple box #2), these set of vectors will be used to verify against the protocol.

Then you have now the right to read the content of the five purple boxes, labeled from 1 to 5. The first box define the “Verification Plans”, the second the “Test Environments”, the third the “Checks” and so on…

I have checked a very interesting point about Synopsys VIP business strategy: I was under the impression that Synopsys’s VIP products were included into the DesignWare IP product, thus Synopsys customer would have benefited from “free” VIP. In fact this is completely wrong, as customer have to acquire Synopsys VIP product (different from the DesignWare IP product), thus Synopsys is really valuing VIP as it should be and create a real business around VIP. As far as I am concerned, I am always suspicious about “product for free”. Yes, you don’t pay for it. But you probably can’t expect a high quality level of support for something you don’t pay for… This is not the case with Synopsys VIP: the company heavily invests to develop the various VIP products; you pay for a quality bunch of product and support, allowing the company to develop new products.

From Eric Esteve from IPNEST

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.