PCIe is familiar to legions of PC users as a high-performance enabler for expansion slots, especially GPU-based graphics cards and M.2 SSDs. It connects higher-bandwidth networking adapters and niche applications like system expansion chassis in server environments. Each PCIe specification generation has provided a leap in bandwidth, with speeds doubling about every two years. The latest PCIe 7.0 reaches 128 GT/sec link speeds, and combined with PHY improvements, PAM4 signaling, and improved error correction introduced in PCIe 6.0, a chip-to-chip use case, at least in moderately-sized, reasonably-priced systems, is emerging.

A recent Synopsys webinar discusses the implications of releasing the 0.9 version of the PCIe 7.0 specification to PCI-SIG members. It’s a conversation between Madhumita Sanyal, Director of Technical Product Management, High Performance Computing IP Solutions at Synopsys, and Richard Solomon, Technical Product Manager, PCI Express Controller IP at Synopsys, who also serves as vice-president of the PCI-SIG. Solomon dives deeper into what makes PCIe 7.0 faster, how that changes the controller logic, and what that will mean for SoC designers.

Faster PCIe 7.0 is good, but it’s not the real news

Solomon starts on a self-deprecating note, saying that PCIe 7.0 is “kind of boring, and boring in a good way.” His point is that if engineers have designed PCIe 6.0-compliant links, they’re already compliant with PCIe 7.0, except now they can access the 128 GT/sec rate. “From a spec perspective, [this is] really very straightforward,” he adds.

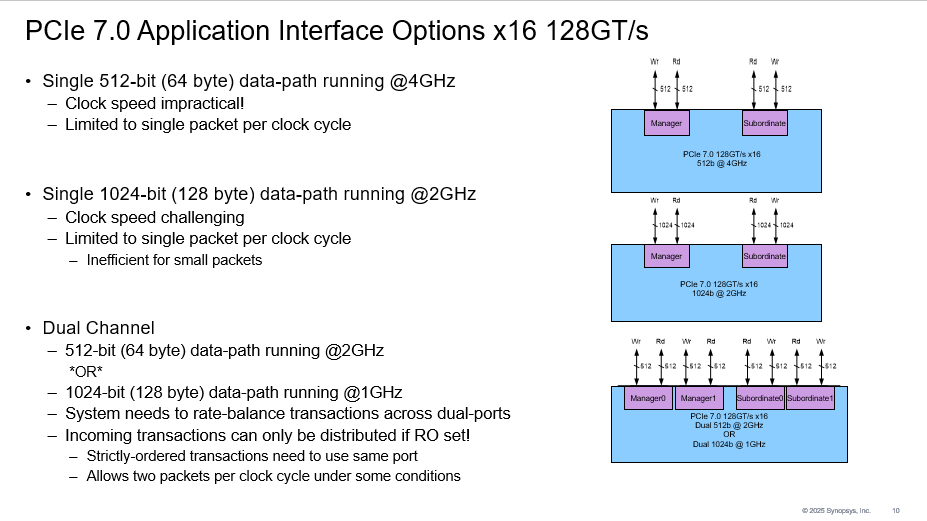

The real challenge with PCIe 7.0 may not be in the links, but in the link managers. “It’s harder and harder for devices to satisfy [bandwidths] with sort of one agent internal, like within an SSD. You’re going to need multiple channels or multiple data movers to sustain the full data rate.” As with so many connectivity schemes, running one link fast is tempting, but designing a chip with more application interfaces spread out at lower clock speeds is less risky. His example cites moving from an unsustainable 512-bit path at 4 GHz to a dual-ported 1024-bit path at 1 GHz.

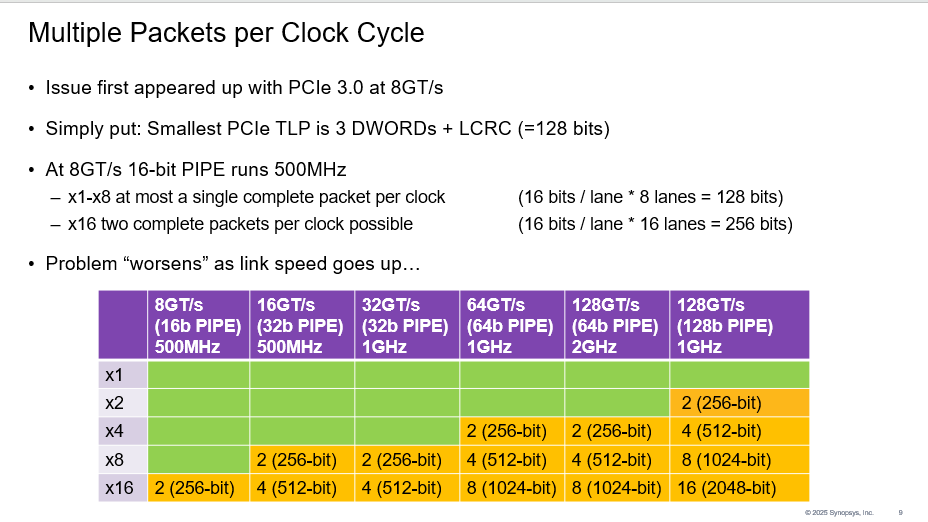

With 1024-bit data paths, the problem becomes multiple PCIe packets arriving per clock cycle, pushing designers into the dual interface solution leveraging PCIe relaxed ordering.

Solomon then launches into an extended discussion of bifurcation and the challenges for PCIe switch designers dealing with many different links. He points out that 512 bits is a magic width fitting a CPU cache line, so moving to two cache lines per clock introduces some concern. “We’re all in this sort of tug of war – it’s not which one of these options you prefer, it’s which one you dislike less,” he muses. However, the difficulty of implementing a 4 GHz clock in current ASIC technology dominates the tradeoffs.

SoC designers get more options with PCIe 7.0

Earlier in the webinar, Solomon points out that PCIe may not be the fastest possible solution, but it’s the fastest at a reasonable price, and he implies that it also gives SoC designers flexibility in architectural choices for systems. He sees AI as a good example. PCIe probably won’t be the choice for a system with thousands of AI chips interconnected, but he believes it’s a clear choice for a system with tens of chips. The bandwidth, low latency, and lower pin count of PCIe 7.0 compared with a parallel PCI-X bus are strong arguments.

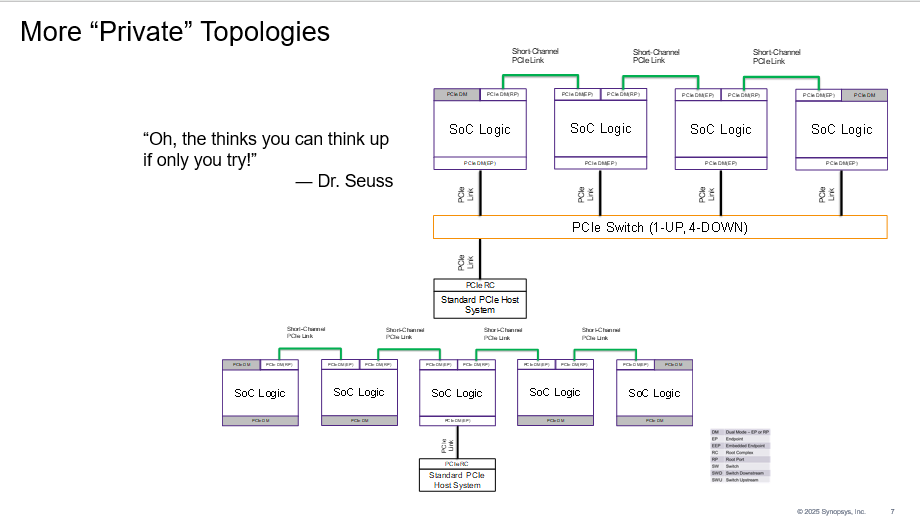

The last few minutes of the conversation discuss the idea of an open ecosystem, like commercial chips with PCIe 7.0 as their interface, versus what internal teams might do with PCIe 7.0 in proprietary ASIC designs in private topologies. “All the tools to analyze a PCI Express channel exist,” he says. “I can use the open nature of PCI Express, but I can also cheat, I can do whatever I want [in a proprietary design].”

The webinar wraps up with questions, like one from an SSD designer who is just launching PCIe 6.0 products and is worried about PCIe 7.0 and even PCIe 8.0 making it prematurely obsolete. With the spec on a two to three-year cadence, that’s not a new concern, and there’s the balance between placing a big bet, leaping to the latest IP in a new chip, or staying put with existing chips and capturing revenue sooner while the ecosystem for the new spec stabilizes.

There’s much more detail in the complete discussion, available online.

Webinar: PCIe 7.0? Understanding Why Now is the Time to Transition

Also Read:

SNUG 2025: A Watershed Moment for EDA – Part 2

Automotive Functional Safety (FuSa) Challenges

Scaling AI Infrastructure with Next-Gen Interconnects

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.