When contemplating the Lego-like hardware and software structure of a leading system-on-chip (SoC) design, a mathematically inclined mind might marvel at the tantalizing array of combinatorial possibilities among its hardware and software components. In contrast, the engineering team tasked with its validation may have a more grounded perspective. Figuratively speaking, the team might be more concerned with calculating how much midnight oil will need to be burned to validate such a complex system.

The numerous interactions between hardware components such as large arrays of various processor types, memory types, interconnect networks, and a wide assortment of standard and custom peripherals and logic, with those of the software, like bare-metal software, drivers, and OS hardware-dependent layers, demand exhaustive functional verification. This process is computationally intensive, requiring billions of cycles to establish confidence in a bug-free design before manufacturing. The challenge is magnified by the relentless pace of technology, with new hardware and software versions constantly emerging while support for older iterations persists.

The Economies of Design Debug

A well-known axiom in the field of electronic design emphasizes that the cost of fixing a design bug soars an order of magnitude at each successive stage of the verification process. What might cost a mere dollar to correct at the basic block-level verification stage can skyrocket to a million dollars when the issue surfaces at the full SoC level, where hardware and software tightly interact.

The stakes become even higher if a design flaw goes undetected until after silicon fabrication. Post-silicon bug detection not only challenges engineering teams but can also lead to exorbitant costs that may drain a company’s financial resources. For small enterprises, such a scenario could be catastrophic, potentially leading to bankruptcy due to the redesign expenses and missed revenues caused by delayed product launches.

In the fiercely competitive semiconductor industry, the margin for error is razor thin. Therefore, rigorous verification at each stage of the design process is not just a best practice—it’s a critical safeguard against the potentially ruinous consequences of post-silicon bug detection.

On the bright side, the electronic design automation (EDA) industry has been investing heavily in resources and innovation to tackle the challenge of pre-silicon verification. The Shift-Left verification methodology is a testament to the industry’s commitment to addressing this challenge.

Arm: Linchpin Example of the Hardware/Software Integration Challenges

Among processor companies Arm is a case-study, because of its vast catalog of IP solutions. Arm offers a wide range of IPs, platforms and solutions, including CPUs, GPUs, memory controllers, interconnects, security, automotive, AI, IoT, and other technologies, each designed to meet the needs of different markets and applications. While the exact number is not publicly known, when adding updates and new releases, it amounts to thousands of different parts.

SoC designers using Arm components face an uphill verification challenge. Once they have selected the IP components, they must integrate them into complex SoC designs, add a software stack to bring the design to life, and ensure compliance, that is, compatibility or interoperability of the software with the hardware.

This process is fraught with uncertainties and risks.

Often, root causes of integration issues can be traced to non-compliant hardware, such as non-standard PCIe ECAM, PCIe ghost devices, or customized components like universal asynchronous receiver-transmitters (UARTs) or GICs. These issues can lead to design malfunctions, and potentially to serious failures. For instance, systems with complex PCIe hierarchies may lack firmware workarounds, custom OS distributions may receive limited security updates, and Windows servers and clients may be incompatible with non-compliant PCI ECAM.

To address these issues, a widely used but increasingly outdated method in the electronics industry is post-silicon testing. While it serves the purpose of debugging hardware flaws after fabrication, it is inherently inefficient. This approach contradicts the well-established principle of exponential cost increase, summarized by the phrase “the sooner, the cheaper.” By delaying the detection of design flaws until after silicon manufacturing, companies incur costly silicon re-spins and face extended timelines.

Fortunately, these issues can be mitigated much earlier in the development cycle through pre-silicon design verification. Pre-silicon verification, which includes simulation, emulation, formal and timing verification, allows engineers to identify and resolve problems before chips are fabricated, significantly reducing both costs and risks.

Arm’s Game-Changing Solution: From ServerReady to SystemReady

To mitigate this challenge, specifically to eliminate or at least reduce design re-spins and accelerate time-to-market, Arm introduced the SystemReady Certification Program in 2022. Building on the success of the ServerReady program, which was launched in 2018 and targeted server applications, SystemReady expands the coverage to include designs like edge devices, IoT applications, automotive systems, and more.

In general, hardware platforms provided by semiconductor partners come with their own software stacks, i.e., firmware, drivers and operating systems. These are often siloed, creating challenges for OS vendors and independent-software-vendors (ISVs) who need to run applications across different platforms, as these setups tend to be highly specific and fragmented. SystemReady aims to break down these silos, enabling software portability and interoperability across all Arm-based A-Class devices. When third-party operating systems are run on devices complying with a minimum set of hardware and firmware requirements based on Arm specifications, they boot seamlessly, and applications run smoothly.

SystemReady Program Foundation

The foundation of the Arm’s SystemReady program lies in two key specifications. First, the Base System Architecture (BSA), a formal set of compute platform definitions to encompass a variety of systems from the cloud to the IoT edge, ensures that in-house developed or 3rd-party sourced software works seamlessly across a universe of Arm-based hardware. Second, a set of accompanying firmware specifications called the Base Boot Requirements (BBR), complements the BSA definitions. These sets of rules are encapsulated in the BSA Compliance Suite, accessible on GitHub.

The suite is designed to run compliance tests during pre-silicon validation, eliminating the need for executing full operating systems to validate the environment. This early-stage validation prevents costly silicon respins, expedites system-level debugging, and accelerates time-to-market.

Arm’s Thriving SystemReady Partner Ecosystem

To reach a vast and diverse customer base while considerably enhancing the value of the Arm ecosystem, Arm has strategically partnered with a wide array of companies, including leaders in EDA, IP, and silicon providers. These collaborations play a critical role in driving the success of Arm’s SystemReady program, a certification initiative that ensures seamless compatibility across hardware platforms and software stacks.

Leading EDA Firms Accelerate SystemReady Certification Success

The pre-silicon validation of software stacks on newly designed hardware platforms demands hardware-assisted verification platforms, such as emulation and FPGA prototyping. These platforms are crucial for ensuring that new designs function correctly across the range of real-world conditions they will face. Best-in-class emulators and FPGA prototypes support comprehensive verification and validation processes, including hardware debugging, hardware-software co-verification, power and performance analysis, and even post-silicon testing for final checks.

Prominent suppliers of hardware-assisted verification platforms have joined Arm’s SystemReady program to enable their customers developing Arm SoCs and components to validate BSA compliance on HAV platforms using Transactors and Verification IPs. By participating in this program, EDA companies enable developers to validate software before silicon is even taped out, significantly reducing risks and development costs while accelerating time-to-market. The “PCIe SystemReady Certification Case Study” is an example of how a collaborative approach to pre-silicon validation can lead to successful certification and market-ready products.

Case Study: PCIe SystemReady Certification

The PCIe protocol is one of the most widely adopted and popular interfaces in the electronics industry, supporting a broad spectrum of applications, including networking, storage, GPU accelerators, and network accelerators. Each of these applications has distinct workload profiles that interact uniquely with system components, making PCIe a versatile yet complex protocol to integrate into hardware platforms.

Arm’s SystemReady certification program for the Arm architecture implementation including the complex PCIe subsystems is designed to ensure that these diverse applications can run seamlessly across various hardware environments. Achieving this certification requires adherence to a stringent set of compliance rules. These rules involve injecting specific sequences into the PCI port and monitoring responses at the PCI protocol layer, ensuring that the system can handle different types of workloads in real-world scenarios.

Synopsys and PCIe SystemReady Compliance

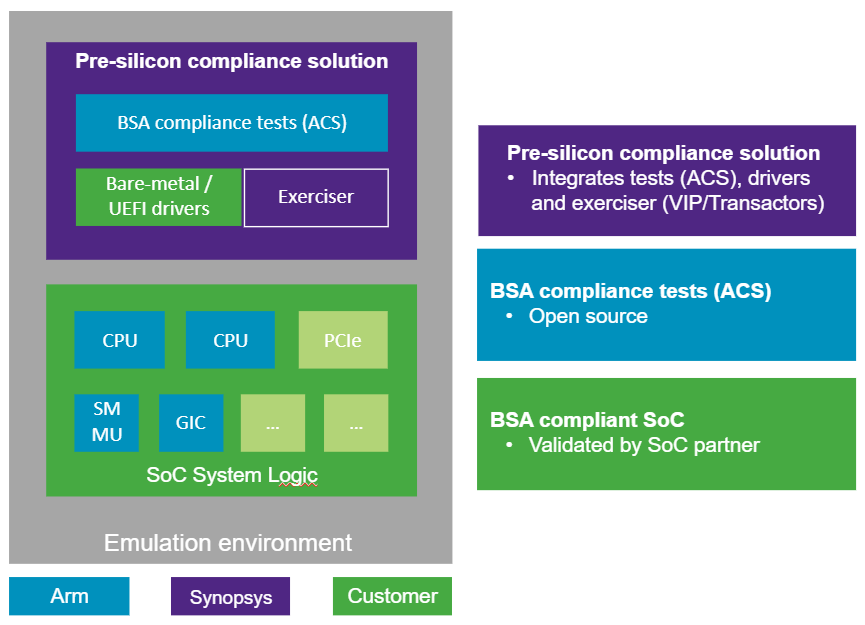

To streamline this process, Synopsys provides a PCI endpoint model specifically designed to meet Arm’s BSA certification standards. As shown in Figure 1, the SystemReady compliance program is a collaborative effort between Arm, Synopsys, and silicon providers. While the silicon partner focuses on developing the boot code, Synopsys contributes the Platform Abstraction Layer (PAL), a crucial software component that ensures smooth execution of Arm’s Compliance Suite tests on the SoC.

The PAL acts as an intermediary, enabling the Compliance Suite to communicate effectively with Synopsys’ transactors and Verification IPs (VIP) thus maximizing test coverage and capturing corner cases that may otherwise be overlooked. This integration ensures thorough testing of PCIe subsystems, providing developers with the confidence that their designs meet the highest standards of compatibility and performance.

Performance Verification and PCIe Protocol Evolution

In addition to compliance testing, performance verification is a critical aspect of pre-silicon design validation for PCIe interfaces. When systems upgrade to newer PCIe protocol generations, such as moving from PCIe Gen 5 to PCIe Gen 6, it involves significant investment. However, it’s vital to verify that the system is fully equipped to handle the additional bandwidth and performance enhancements offered by the newer protocol. Performance validation helps determine whether a developing SoC can manage various workloads and uncover any potential bottlenecks that might prevent the system from realizing the full benefits of the upgrade.

Synopsys’ support for integrating the Compliance Suite adds an additional layer of performance validation, allowing users to run comprehensive performance scenarios, particularly focused on the PCI subsystem. This ensures that the PCIe subsystem not only complies with Arm architectural requirements but also achieves optimal performance across a range of SoC applications.

Conclusion

By ensuring that software stacks are portable and interoperable across a diverse range of platforms—from cloud servers to edge devices and IoT applications—Arm’s SystemReady program plays a pivotal role in minimizing design risks. This standardization significantly reduces design costs and accelerates time-to-market, enabling companies to deliver products that function seamlessly out-of-the-box.

SystemReady not only enhances design efficiency but also opens new avenues for Total Addressable Market (TAM) expansion. By ensuring compatibility and reducing development complexity, the program allows Arm’s partners to target a broader range of industries and applications, providing them with a distinct competitive advantage.

These efforts underscore Arm’s commitment to empowering its ecosystem and driving innovation across the industry.

Also Read:

The Immensity of Software Development the Challenges of Debugging (Part 1 of 4)

The Immensity of Software Development and the Challenges of Debugging Series (Part 2 of 4)

The Immensity of Software Development and the Challenges of Debugging (Part 3 of 4)

The Immensity of Software Development and the Challenges of Debugging Series (Part 4 of 4)

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.