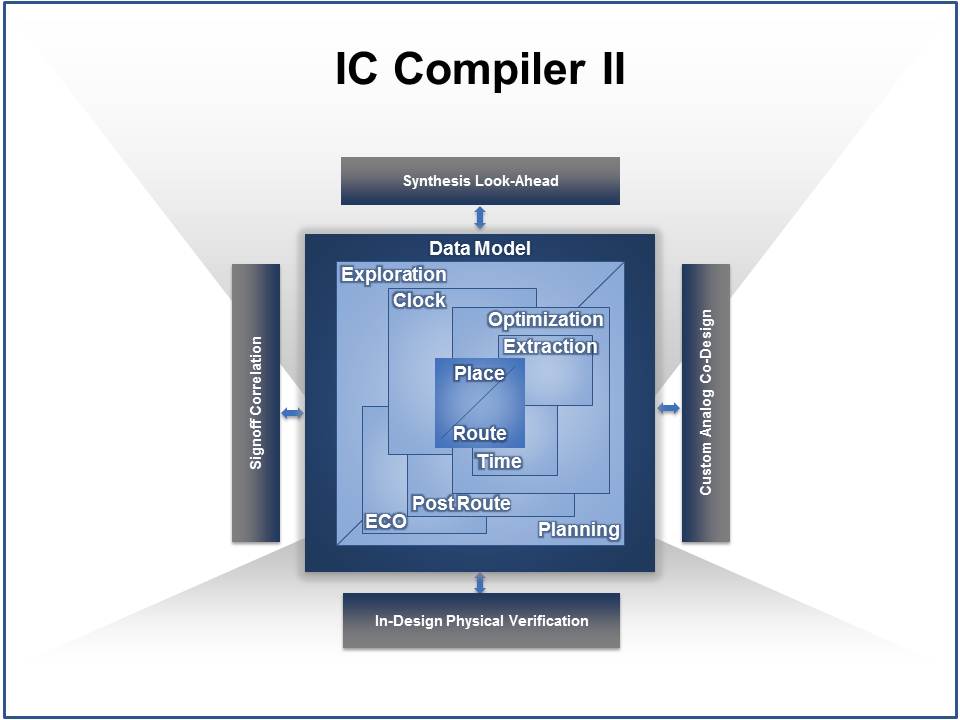

EDA start-up companies often have the advantage over established vendors by being able to start from scratch, instead of having to maintain some legacy code that no longer is competitive. But what happens when the established vendor decides to rewrite their IC implementation tools from scratch? In this case it’s good news, because Synopsys has just announced a rewrite of their popular IC Compilerand have dubbed it IC Compiler II. I talked with Saleem Haider of Synopsys earlier this month by phone to get briefed about it.

There are many motivators to rewrite a place and route toolset:

- Increased competition from Mentor, Cadence and AtopTech

- Larger design sizes

- Concurrent analysis requirements

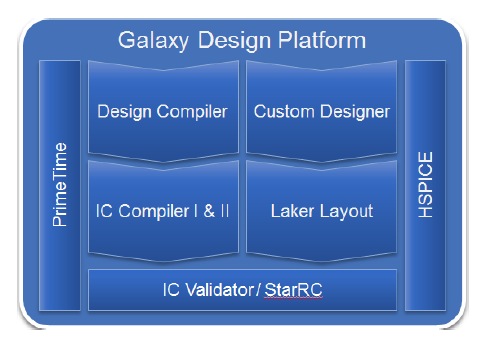

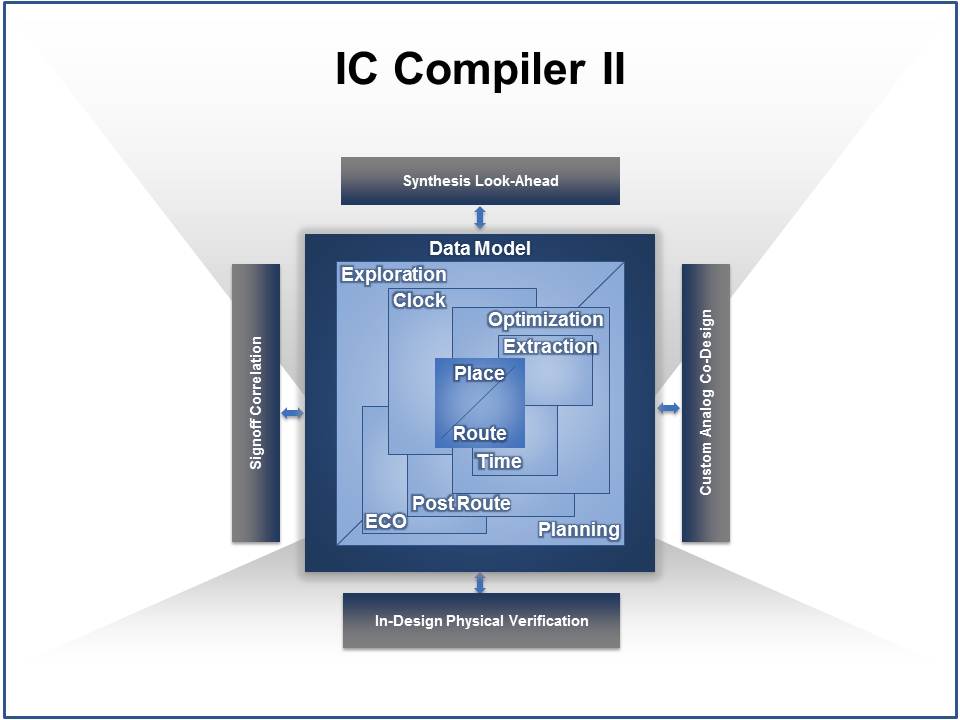

SoC designs can now have millions of cells per layout partition, and the total time to complete a place and route run could take days, so any new tool that can reduce that time and effort is certainly going to be attractive. The original IC Compiler and new IC Compiler II tools will continue to be offered, although you’ll have to pay an upgrade fee to get the benefits of IC Compiler II. Here’s the big picture of IC implementation tools at Synopsys where IC Compiler is one of the pieces:

The promise of IC Compiler II is that throughput can be 10X faster, using 5X less RAM resources, and producing the same or improved QOR (Quality of Results). With those improvements a design team can cut down their project schedule, spend more time to achieve a higher frequency, get a smaller area, do more exploring, or even use fewer engineers. Early customers of IC Compiler II are taping out real designs in Q1, Q2 and throughout 2014.

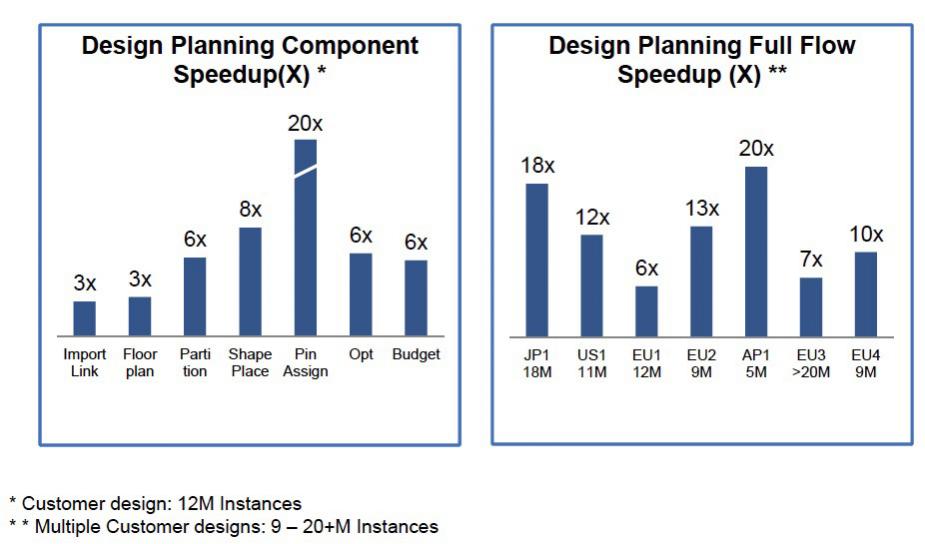

This rewrite of IC Compiler has been going on for years now and included re-using some of the database concepts from the acquired Magma tools, creating a new infrastructure, reworking the engines (Timer, Hierarchy, Optimization, Clocking) and re-using code (CGPL placer, Zroute). The Milkyway database on disk is replaced by the Magma approach, and all of the interfaces are standard formats (Verilog, lib, lef, def, tf, tlu+, SDC, upf). Hierarchy is supported for both logical and physical operations, and the capacity handles 500 million cells. Examples of design planning speedups from several customers:

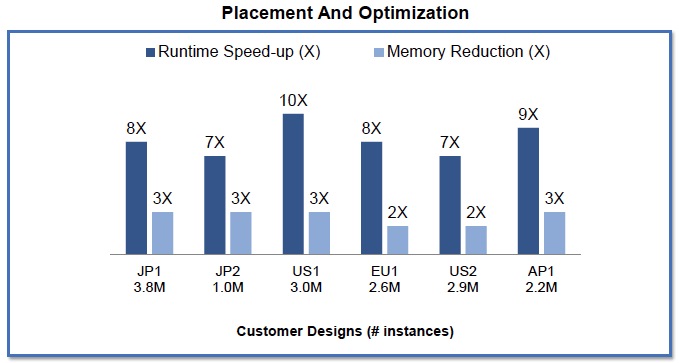

For optimization the engineers created APS – Analytical Physical Synthesis, and it does global optimization along with being multi-threaded. Routing re-used Zroute for global-route. Analysis for multi-corner, multi-mode and multi-voltage was also new. The clock tree construction is all new and is MCMM (multi-corner, multi-mode) driven, uses global optimization, and concurrently accounts for both data and clock signals. Placement and optimization improvements on customer designs show both runtime speed-up and memory reduction:

Summary

Synopsys has managed to rewrite their flagship IC Compiler so SoC designers now get to choose between using the first generation or second generation version for place and route. Early customers include: Imagination Technologies, LSI Corporation, Panasonic, Samsung and STMicroelectronics. The actual production release of IC Compiler II is around the DAC time frame, and if your present P&R run times are slowing down your project schedule then it makes sense to give this new tool a look. Learning the IC Compiler II tool should be easy for existing IC Compiler users.

lang: en_US

Share this post via:

Comments

0 Replies to “IC Implementation Tool Gets a Rewrite, Now 10X Faster”

You must register or log in to view/post comments.