It’s a matter of pride to me and many others from Atrenta days that the brand we built in SpyGlass has been so enduring. It seems that pretty much anyone who thinks of static RTL checking thinks SpyGlass. Even after Synopsys acquired Atrenta, they kept the name as-is, I’m sure because the brand recognition was so valuable.

Even good things must evolve. Synopsys verification has a strong “VC” brand and it was natural that SpyGlass should fold in under this, still with a strong connection to its founding identity. So now we have VC SpyGlass, in line with VC LP and VC Formal.

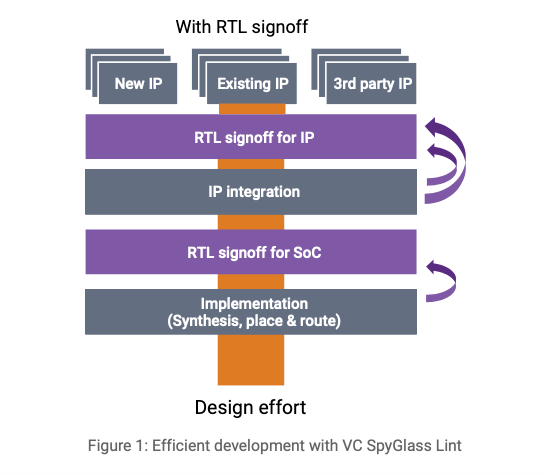

This isn’t just a rebranding. Synopsys have put a lot of work into this next generation SpyGlass, including 3X performance increase in half the memory, always a plus in any context and especially valuable when you want to screen full-chip RTL. But there are a number of other significant advantages which resonate all too clearly from my time at Atrenta.

One is a 10X reduction noise. Anyone who’s ever used a static verification tool knows that noise can be a huge pain. Simulation will only catch bugs exercised and detected by the tests you run. Static verification will catch all bugs within the range of checks it performs. But the devil’s bargain you make for this completeness is that it will also catch many things that aren’t problems or are just different manifestations of a problem it already reported. You may have to wade through a whole bunch of spurious errors to find the one or two real problems you need to fix.

Reducing this noise level is a very big deal. I remember the Atrenta team working on methods to compress errors by root cause as one approach to noise reduction. Other techniques used formal methods to weed out structurally apparent errors which are not functionally possible. It sounds like Synopsys has extended these methods further.

Another key advantage I cannot over-emphasize is completing compatibility with the Synopsys implementation tools. This starts with synthesis compatibility. Under the hood, SpyGlass does a quick synthesis so it can run a lot of checks on an elaborated graph. How effective (or noisy) that is depends very much on how well it mirrors the ultimate real implementation. At a superficial level that’s not such a big deal. You use one of the standard open-source synthesis platforms and you’re good, right?

Wrong. There are a number of places where using a different synthesis solution is likely to generate false errors or miss real errors: datapath and mux inferencing are just two examples. When a tool gets this stuff wrong, pretty soon it’s thrown out. We always wrestled with trying to match DC behavior as closely as we could, but you can never do as well as you can when using the real thing. No longer a problem in VC SpyGlass.

Another related problem was matching behavior in constraints. There’s a lot of useful information in those constraints to flag clocks, resets and so on. Especially useful in CDC and reset analysis and can also be useful in other aspects of static analysis. When is a clock really a clock? You can try to infer this bottom-up by just looking at the RTL, tracing back from register clocks. But that’s not foolproof. Constraints fix the ambiguity, but you need to interpret them the same way the implementation tools do. Not so bad in vanilla SDC but potentially much more difficult in Tcl. Again, no longer a problem in VC SpyGlass.

Finally, VC SpyGlass has unified debug with Verdi. Let’s face it, Verdi is the de facto standard for functional debug in the industry. Everybody uses it. We had an interface to Verdi when I was at Atrenta. But there are interfaces and then there are native integrations. Native integrations are invariably faster and more capable. You can switch back and forth between VC tools, retaining a consistent VC interface throughout.

I’m happy to see VC SpyGlass fully integrated the VC family. It confirms the value we created and a continuing bright future for the technology. You can learn more about VC SpyGlass HERE.

Also Read:

Prevent and Eliminate IR Drop and Power Integrity Issues Using RedHawk Analysis Fusion

Achieving Design Robustness in Signoff for Advanced Node Digital Designs

Navigating Memory Choices for Your Next Low-Power Design

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.