If you have ever send a Request For Quotation (RFQ) for an ASIC including processor IP core, memories, Interfaces IP like PCIe, SATA or USB and Analog function like Analog to Digital Converter (ADC) or Digital to Analog Converter (DAC), you have discovered, like I did a couple of years ago, that these Analog functions may be the key pieces, limiting your choice of the technologies and foundries. Every System-on-Chip (SoC) will use a processor IP core (and most of the time it will be an ARM core, by the way), so you will realize that the processor is not a problem as it will be available in most of the technologies/foundries, as well as any Single Port or Dual Port memory, through memory compilers.

But, especially if you target advanced nodes like 28 nm, being able to find the right ADC or DAC may become a real issue. If you can’t find it in the technology you have to target, for good reasons like benefiting for the smallest possible area, or device cost, or to make sure that the power consumption will be within the allocated budget, the only possibility will be to order a custom design… not really the best approach to minimize risk and time-to-market (TTM)! When a well-known and respected IP vendor like Synopsys announce they have scaled their ADC Architecture to support Mobile and Multimedia SoC at 28 nm –and beyond, that’s the type of news which make your life easier when sending ASIC RFQ, targeting to use TSMC 28 HPM. If it’s your case, that make sense to attend to the next webinar:

Scaling ADC Architectures for Mobile & Multimedia SoCs at 28-nm and Beyond

If you are interested, you should quickly register as this webinar will be held on Tuesday, the 10[SUP]th[/SUP] of September…

Overview:

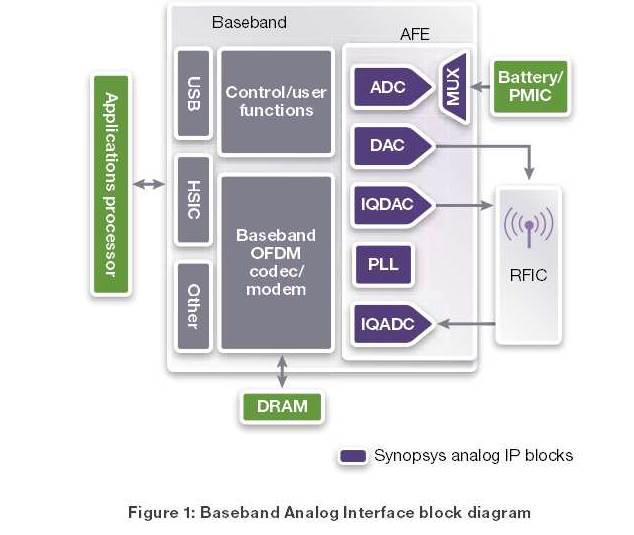

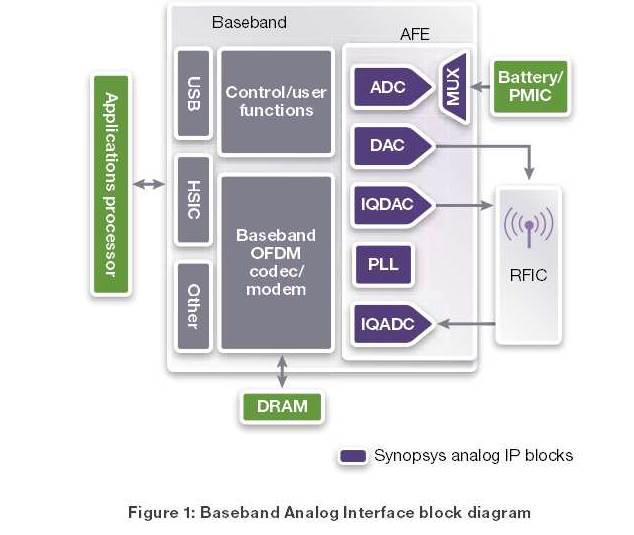

Data converters are at the center of every analog interface to systems-on-chips (SoCs). As SoCs move into 28-nm and smaller advanced process nodes, the challenges of integrating analog interfaces change due to the process characteristics, reduced supply voltages, and analog blocks’ area requirements. Synopsys is offering a complete portfolio for analog interfaces in 28-nm includes high-speed ADCs and DACs, PLL, and general-purpose ADCs and DACs, implemented on a Standard CMOS process with no additional process options.

I have noticed a few impressive features:

- Parallel SAR 12-bit ADC architecture implementations for up to 320 MSPS sampling rates

- Parallel assembly allows for greater architectural flexibility for specific applications

- Very high performance 12-bit 600 MSPS DAC

- Power consumption reduction of up to 3X and area use reduction of up to 6X over previous generations

This webinar will:

- Compare the prevailing analog-to-data converter (ADC) architectures in terms of speed, resolution, area, and power consumption trade-offs

- Describe the benefits of the successive-approximation register (SAR)-based ADC architecture for the medium and high speed ADCs

- Describe how implementations of the SAR ADC architecture can reduce power consumption and area usage for 28-nm process technologies

- Present the 28-nm DesignWare® Analog ADCs, which use the SAR-based architecture, and explain how they achieve 3x lower power consumption and 6x smaller area compared to previous generations

Who should attend: SoC Design Engineers, Managers and System Architects

Presenter:

Carlos Azeredo-Leme, Senior Staff Engineer, DesignWare Analog IP, Synopsys

Carlos Azeredo-Leme is a senior staff engineer for the DesignWare Analog IP at Synopsys since 2009. Prior to joining Synopsys, he was co-founder and member of the Board of Directors of Chipidea Microelectronics in 1993, where he held the position of Chief Technical Officer. There, he was responsible for complete mixed-signal solutions, analog front-ends and RF. He worked in the areas of audio, power management, cellular and wireless communications and RF transceivers. Since 1994 he holds a position as Professor at the Technical University of Lisbon (UTL-IST) in Portugal. His research interests are in analog and mixed-signal design, focusing on low-power and low-voltage. Carlos holds an MSEE from Technical University of Lisbon (UTL-IST) in Portugal and a Ph.D. from ETH-Zurich in Switzerland.

Eric Esteve from IPNEST

lang: en_US

Share this post via:

Comments

0 Replies to “Searching an ADC (or DAC) at 28 nm may be such a burden…”

You must register or log in to view/post comments.