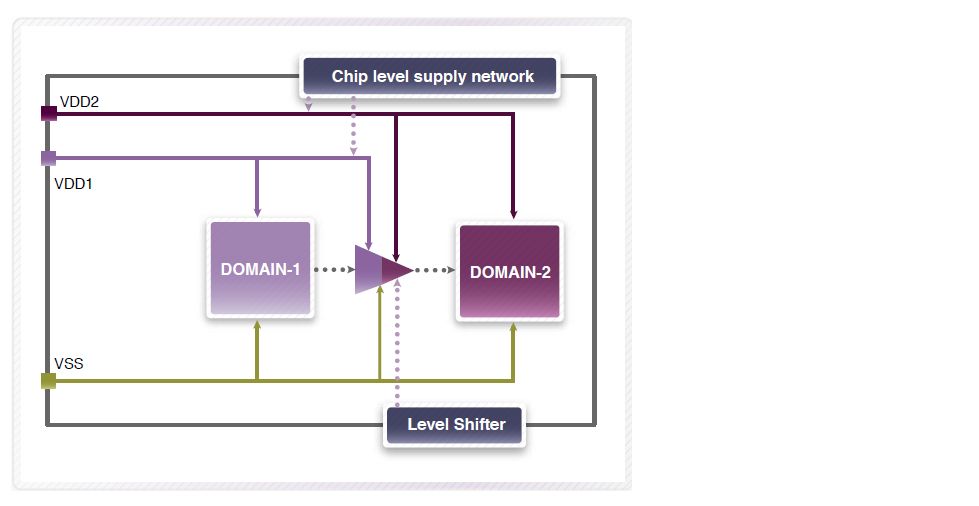

The burgeoning need of high density of electronic content on a single chip, thereby necessitating critical PPA (Power, Performance, Area) optimization, has pushed the technology node below 0.1 micron where static power becomes equally relevant as dynamic power. Moreover, multiple power rails run through the circuit at different voltages catering to analog as well as digital portions of the design. Pins in a gate can be driven by power rails at different voltages. IP blocks such as ARM micro-processors typically come with multiple power rails and also in-built power domains for power management of the blocks. The network according to its logical portions driven by particular supply nets is divided into different power domains, all of which may not be active at the same time. Any un-required domain can remain off hence saving the power. Various techniques and different types of multi-rail cells such as level shifters, power switches, isolation cells etc. are employed to manage power.

Tools must be capable of dealing with multiple power rails and intelligently associating logic with their respective supply nets. That would mean relating to the voltage levels at various nodes at which the design is operating. Also the connectivity and constraint between supply net and power pin, which depend on the context in which the multi-rail cell has been instantiated, needs to be captured. IPs can have separate internal power switches and logic divided into multiple power regions complicating the matter further.

Synopsys’s Eclypse Low Power Solution provides state-of-the-art verification tools MVSIM and MVRC and necessary infrastructure for complete low power verification. MVSIM accurately verifies all power transitions in succession through various voltage levels. MVRC statically checks for correct implementation of power management scheme. The system provides a comprehensive solution for verifying multi-rail cells at RTL, netlist and at PG-netlist stages of the design flow.

Eclypsecaptures cell level information such as logic to power pin association in Synopsys’s existing Liberty format enhanced with standard low power attributes thus providing consistent, integrated platform for the overall design flow enabling designers work independently at different levels such as chip, RTL or cell level in the flow. Chip level information such as chip-level power rail connection with cell-level power pins is provided in power intent file using UPF (Unified Power Format, IEEE 1801 standard). By using UPF a designer can define complete power architecture of the design; partition the design and assign blocks to various power domains which enable MVSIM and MVRC to infer power pin connections with associated logic. For hierarchical flow, Eclypse provides simple commands to associate inputs and outputs of a block to its power pins.

[Example – multi-rail design]

MVSIM accounts for right analog levels of voltages at various pins and hence can simulate different power techniques such as power gating, dynamic voltage scaling, state retention etc. For IPs it can detect available power-aware models and automatically replace the non-power-aware simulation models with the corresponding power-aware models. It also provides option to choose between power-aware or non-power-aware mode depending on the simulation requirement.

[MVSIM output of multi-rail design – with island_V3 off, instance3 output is corrupted]

MVRC verifies static power management of the design taking care of right connection between pins and their supply nets, right insertions and connections of low power structures like level shifters, power switches, retention registers etc. At RTL level, it combines the cell level information from the library with the chip level information available in the UPF format to determine the associated supply net for each node in the design and report any architectural issues or missing/redundant isolation/level-shifter policies in UPF. Similarly it can check netlist after synthesis or post layout for right power pin connectivity and missing/redundant cells with respect to policies defined in UPF.

A very nice detailed description about the methodology has been provided by Synopsys in its white paper located at Low Power Verification for Multi-rail Cells

Considering analog and digital designs to co-exist with increasing design size and complexity, operating at different voltage levels, it’s inevitable to go without multi-rails that introduce its own challenges to low power verification. Eclypse along with MVSIM and MVRC incrementally adds that extra intelligence into their system of library and chip level infrastructure including UPF to provide a comprehensive solution for static and dynamic power simulation and verification of multi-rail low power circuits.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.