We live in a world run by electronics systems. With the exception of completely isolated systems, all others take inputs, process them and produce outputs. The value of a system is determined not only by how well it processes the inputs but also by how well it handles inputs and outputs. Handling in this context means, how much data can the system take in and how fast can it accurately read inputs and write outputs. That is the reason so much importance has been placed on electronics interfaces over the years.

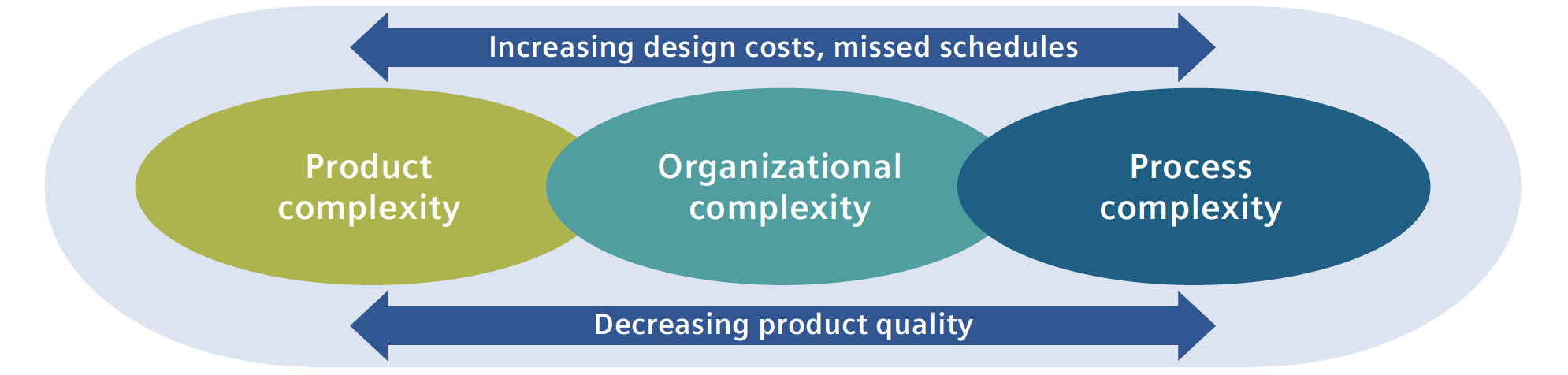

Over time, the industry has introduced a number of different interfaces to satisfy various applications and systems needs. In the age of big data, high performance computing and edge computing, very high-speed interfaces are intrinsic to electronics systems. The demanding data transfer requirements of these systems impose their own complexity factors into electronics systems designs. But the introduced complexities are not just from the tight and demanding specification of the interfaces themselves. The traditional design methodology (process) and design teams (organizational) introduce significant challenges as well. Refer to Figure 1. These challenges cut deep into how successfully and cost-effectively the systems are designed for manufacture. Yet not much attention is focused on these aspects.

Figure 1

Source: Siemens EDA

A recently published whitepaper identifies how these challenges affect a number of phases of the design lifecycle from design definition all the way through to design approval for release to manufacture. The whitepaper is titled “The Design Lifecycle of an Electronics Interface,” and is authored by David Wiens, product marketing manager at Siemens Digital Industries Software. A primer reading material is an earlier SemiWiki blog, “The Five Pillars for Profitable Next Generation Electronic Systems,” which is based off of another whitepaper by David Wiens.

While the earlier whitepaper discusses the full scope of digital transformation needed for next-generation electronic systems design, the latest one focuses on ways to overcome challenges faced during the lifecycle of implementing electronic interfaces.

Design definition and early optimization phase

As the topology of an interface can span across multiple boards, more than one stack-up may be likely and the interconnect topology will include connectors. To ensure optimal performance, it is easy to play conservative and over-specify materials, which will lead to high-cost boards. Tools to allow early exploration of interface interconnect topologies enables optimal termination and decoupling strategies in the context of the chosen stack-ups. With large teams collaborating on complex designs, errors can easily creep in. Errors such as components not properly connected to power or ground, missing power, incorrect diode orientation, missing drivers or receivers and incorrect board-to-board connections are frequently seen with large teams working on complex designs. Rugged tools will catch these errors from propagating to layout.

Interface constraint definition phase

Traditionally, constraints definition and communication among team members have followed a manual approach. This calls for manually converting electrical constraints into their physical equivalents when preparing for layout, thereby restricting the options during layout. Ideally signal integrity analysis should directly generate constraints for topology and impedance. Tools that operate off of a unified constraints playbook and allow multiple members of the team to review and update constraints reduces the chances of errors due to miscommunications among team members.

Mechanical design and component placement phase

As the design of physical boards involves collaboration with teams from various disciplines, a very strong common thread is needed to eliminate the need for frequent data re-entries. A virtual model of the final product that is being designed is called a digital-twin. Tools that work off of a unified data base operating under a digital-twin methodology will serve well to minimize rework once routing starts.

Design approval and release phase

With the design reviewed for performance and manufacturability, the final step involves cost estimates, confirmation of materials and component availability and final management signoff on the design. Traditionally this involves generating and sending various files around to different people but to maintain a common thread approach, everyone should have access to a single unified database.

Tying it all together

The common thread that ties together the entire process and associated teams’ design related activities is made possible through advanced tools. Siemens EDA’s Xcelerator portfolio of tools enables integrated workflows and organizations to deliver digital transformations. Xcelerator technologies that address the challenges in this paper include: the Xpedition Enterprise design flow for electronics systems, NX for mechanical design, Teamcenter for PLM data management, HyperLynx and Simcenter for performance verification, and Valor for manufacturability verification.

Summary

If you are involved in designing electronics interfaces, I strongly recommend downloading and reading David’s complete whitepaper. It contains a lot of objective and compelling details to help you evaluate if any critical changes may be needed in your design process and team deployments.

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era