PCI Express (PCIe) has become an important communication element in a wide range of systems. It is used to connect networking, storage, FPGA and GPGPU boards to servers and desktop systems. It has progressed a long way from its initial parallel bus format. Its evolution to a serial point to point configuration has been accompanied with increased speeds and throughput. PCIe GEN5 boosts individual lane speeds to 32 GT/s, doubling the previous version’s speed. Along with this speed improvement come a number of changes to the specification. Complex new functionality and added clock rates mean that verification has become more difficult. To address these verification needs, Mentor has developed Questa Verification IP (QVIP) for PCIe GEN5 that fully complies with the new spec and can be configured as needed.

Mentor has a white paper titled “Tackling Verification Challenges for PCIe GEN5” that discusses what is new in GEN5 and introduces the case study of a product developed using their QVIP. The authors, Mentor’s Akshay Sarup and Anritsu’s Kazuhiro Fukinuma talk about the five major areas where the specification has changed and then reviews the addition of PCIe GEN5 support to Anritsu’s MP1900A signal quality analyzer.

PCIe GEN5 makes allowances for the PHY layer to be used for other protocols. The PHY can support PCIe and one or more other protocols at the same time. Negotiation for the use of alternative protocols requires the support of Modified TS1/TS1 Ordered Sets (OS) alongside standard TS1/TS2 Ordered Sets. This negotiation occurs at the same time as Lane number negotiation. If the connected port does not support the Modified TS1/TS2 OS, the training reverts to the standard TS1/TS2 OS and switches to the appropriate encodings.

Precoding is available at the 32 GT/s rate to help mitigate issues caused by the -36 dB insertion loss target. With higher decision feedback equalizer tap ratios, certain patterns such as alternating 1s and 0s are susceptible to error propagation on a single bit flip. This can result in CRC errors that can potentially break the CRC detection capability. Precoding performs XORs with the prior bit. Precoding is requested by a receiver prior to entering 32GT/s rate and will stay on for the entire rate setting, until the next equalization.

Equalization is another thing that was changed. Rather than stepping up sequentially through the slower transfer rates, the specification provides for the ability to bypass the slower speeds and move directly to 32GT/s for equalization. Of course, if the equalization fails, the speed is dropped to 8GT/s for equalization. Ports can alternatively advertise that no equalization is needed, and previous saved settings will be applied. Together these additions can shave significant time off the equalization process.

The above changes necessitated changes in the Link Training Status State Machine (LTSSM). Previously reserved bits are now used for new functionality. Also, the sequence of events during training have changed as a result of these new features and the higher operating speed. Added to his are new testability features that allow more flexibility in setting up loopback tests.

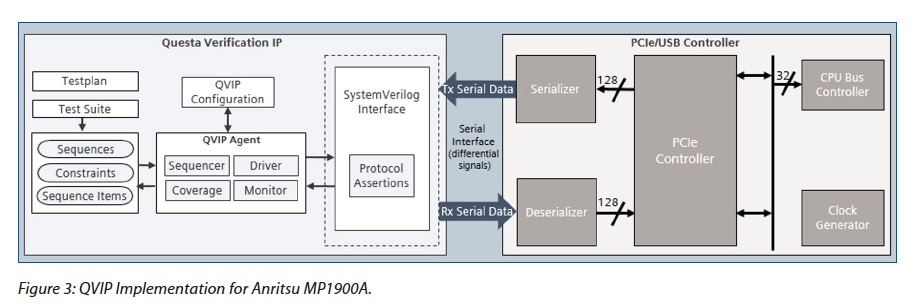

Anritsu, one of the leading companies providing PCIe test and measurement solutions, used Mentor’s PCIe GEN5 QVIP to accelerate the development of new features to support GEN5. With the QVIP’s high configurability they could easily set up parameters any way they needed to set up testbenches. Using assertions, they were able to eliminate a number of subtle design issues early on in the process. The Mentor QVIP includes built-in sequences to allow a quicker ramp up time for users.

The white paper on Verification IP from Mentor does a good job of highlighting the new features in GEN5. It also shows how it was used to provide comprehensive verification by the Anristsu team to deliver a robust signal quality tester. As PCIe grows more complex and sophisticated, the case for Verification IP is becoming pretty clear. The white paper is available for download on the Mentor website.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.