At DACin San Francisco this past June I was able to visit and blog about two dozen EDA companies, however there were so many more products and events to see that I couldn’t possibly have enough time to enjoy them all. Fortunately for me there were plenty of videos made of vendor presentations, so this week I got caught up a bit by watching a video about Methodicsand presented at the Cadence theatre. Methodics is focused on automating the tasks of IP and design management for SoC and any chip design.

IP (Intellectual Property) is defined as everything that enables a design, like:

- PDKs and Libraries

- Memories

- Tools and their versions

- New Blocks

- Derivative Blocks

- Internal & External IP (reusable blocks)

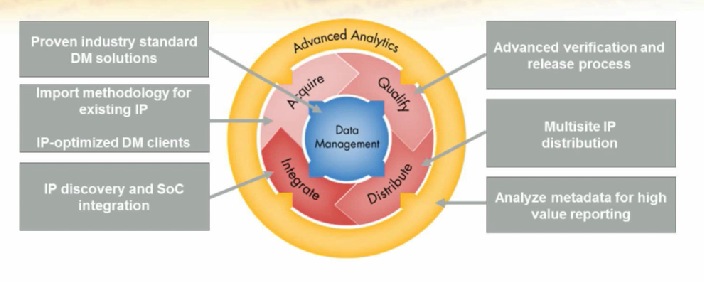

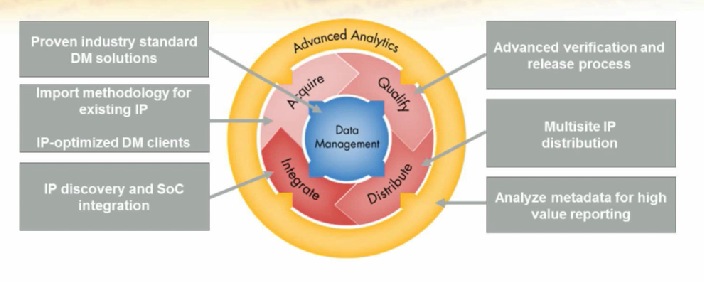

IP blocks go through a natural cycle of being acquired, qualified, distributed and integrated in a project. Even when a project is completed, it can then become a new IP for re-use in the next project. Design Management (DM) tools have been around for awhile, like: Perforce, Subversion, CVS, DesignSync, etc. The Methodics approach is to work with any DM vendor, creating a tool flow that manages the entire design process like this:

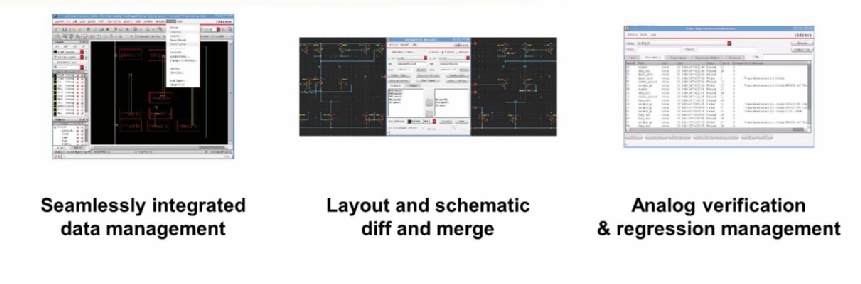

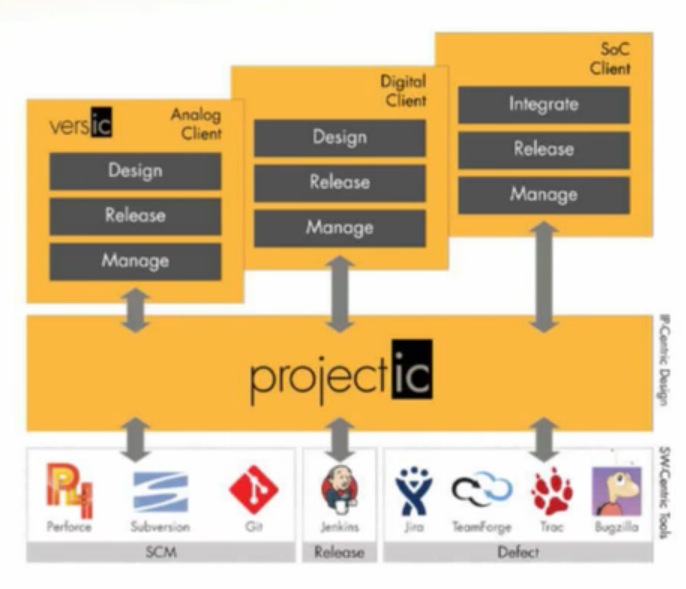

The specific EDA tool name from Methodics is called project IC, and users can control it several ways: a command line interface, web app, a tight integration within Virtuoso, or integrate yourself using APIs. Within Virtuoso an analog designer can Check-in or Check-out cells by using standard menus, run visual diffs on schematics or layouts, plus use analog verification and regression management:

So within Virtuoso a designer can control analog tests and regressions, then see the status of each test over time.

Related: Speeding up IP and Data Management

The modular approach with project IC allows design teams to continue using their favorite DM tools, or add new DM tools like Git or NetApp. IP can be described as a hierarchy of lower-level IP blocks, and you can catalog all of the IP used within your own company to maximize re-use, keep communication updated about the status of all IP blocks, and control the access and permissions of each IP block.

Distributing your specific IP throughout the company worldwide is enabled with the concept of workspaces, where each location has their local repository and it’s all transparent to users.

Defect tracking is linked to each IP block, so you can visually see all bugs for all IP blocks that you are working with. Industry standard bug-tracking tools are used, like: Jira, TeamForge, Trac, Bugzilla. Releasing an IP block is an automated process to allow only good versions to be used. With the analytics and metrics tools you can customize what you dashboard looks like.

Related: Digital, Analog, Software, IP – Isn’t it all just the same?

The big three reasons that engineers are choosing project IC for their IP and Design Management are:

- Open Data

- Open Interfaces

- Open Architecture

Comments

There are no comments yet.

You must register or log in to view/post comments.