At Intel back in the late 1970’s we were designing DRAM chips and mounting them in ceramic and plastic packages, however there were problems when some of the die would crack inside of the package because of thermal mismatch issues with how the die was attached to the heat spreader inside the package. Back then we really didn’t have any computer models of the complex chip to package interface, or any scientific way to simulate the reliability of the packaging process. Fast forward to today and clever computer scientists have indeed figured out a way to model and simulate the reliability of IC packaging. To learn more about these advancements I spoke with Harish Surendranath, an expert at Dassault Systemes (DS). Harish graduated in 2001 with an MS degree in Mechanical Engineering and joined ABAQUS Inc, which was then bought by Dassault Systemes in 2005.

When I talk about the mechanical reliability of IC packaging there are several areas of concern:

- Thermal cycling

- Moisture sensitivity

- Vulnerability to shock and drop

- Package to board interconnects

- 2.5D and 3D packaging issues

- Use of TSV and silicon interposers

- Electromigration

Instead of the old-fashioned method of building a prototype and then testing it, you can instead do a virtual product qualification which should not only save you a lot of time but also provide detailed insights regarding the response of the package, helpful in ensuring the reliability. SIMULIA is DS’s brand for realistic simulation. Abaqus Unified FEA (Finite Element Analysis) from SIMULIA is used widely in the industry to improve the reliability of packages. As packages become more complex, weak spots increase exponentially. Simulation is critical to understanding the response under different operating conditions so that you can modify the design to avoid potential failures.

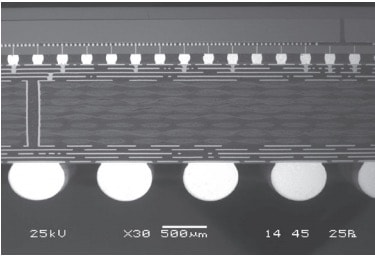

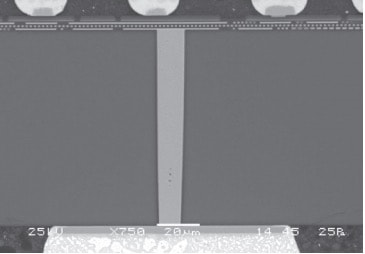

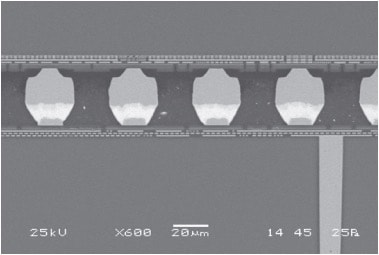

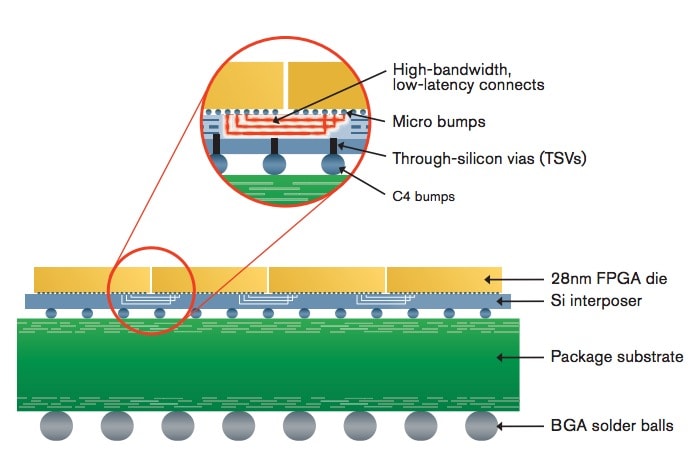

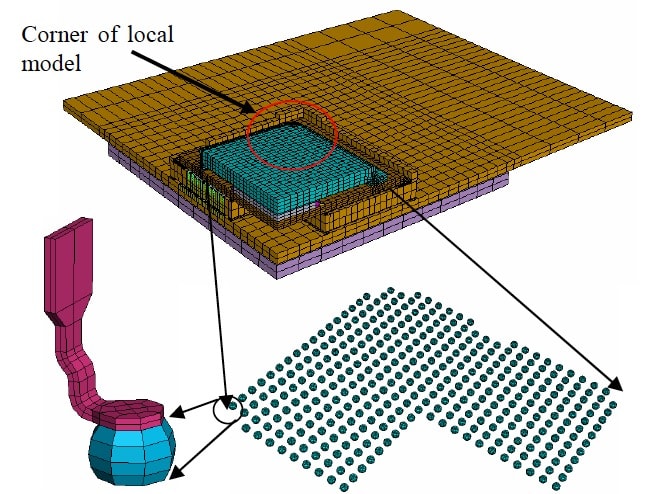

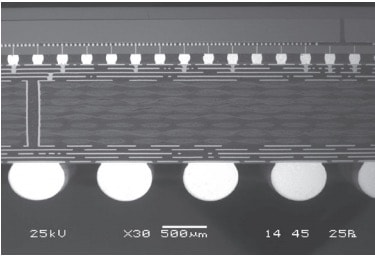

Xilinx is a user of the SIMULIA software and they used Abaqus for package thermomechanical simulation and analysis in 2011 for their four-slice 28nm chip mounted on a silicon interposer with thousands of micro-bumps.

Overall Assembly. Source: Xilinx

TSV Interposer

Micro-bumps

Package thermomechanical simulation and analysis were run with Abaqus using 3D models to help understand warpage of the package during thermal stressing. Here’s a schematic of the package configuration:

DS has collaborated with industry leaders and research institutions for over 20 years to apply and enhance simulation technology to improve package reliability. Engineers from Intel and DS wrote a paper at the 2007 ASME International Mechanical Engineer Congress and Exposition on the topic of modeling for solder joint fatigue reliability. They analyzed a land grid array (LGA) socket with its package, where solder balls are attached on J-lead paddles:

LGA socket with its package

The direct cyclic procedure combined with a global-local approach in Abaqus were used to predict the failure location of on the ball and a more accurate mechanical response of the BGA during fatigue.

Accurate characterization of power supply systems necessitates electromagnetic field simulations to take into account various electromagnetic interactions in packages. The importance of using a 3D field simulator is related to the multilayer stack-up, none-ideal return current paths and the presence of three dimensional geometries such as BGAs and bond wires. DS partner CST provides engineers access to a 3D full wave simulation. This partnership was announced in May of last year.

As you can imagine, these full 3D simulations are very compute intensive so the solver technology has been parallelized so that a typical simulation can be run on 16 to 32 cores or more and you get results in hours. With each new generation of workstations these simulation approaches for package reliability are more practical than ever.

Further Reading

- Abaqus Unified FEA

- Temperature Cycling Analysis of Lead-Free Solder Joints in Electronic Packaging

- Investigation of moisture-induced delamination failure in a semiconductor package via multi-scale mechanics

Also Read

Semiconductors and Conflict Minerals

An Easier Way to Reach Design Closure for SoC

How Can Big Data and EDA Tools Help?

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era