Digital verification engineers have developed robust, thorough metrics for evaluating design coverage. Numerous tools are available to evaluate testbenches against RTL model descriptions — e.g., confirming that simulation regressions exhaustively exercise signal toggles, RTL statement lines, individual statement sub-expressions, individual conditional paths in a case or if/then/else construct, etc. Hardware description language standards have evolved to include (non-functional) statement definitions that allow verification engineers to add specific, complex measurement tests — e.g., asserts, covergroups.

Digital verification teams have also often deployed methods to track coverage progress throughout the design cycle, to identify areas in the overall design where additional (directed or biased-random) testcases need to be written and added to the verification suite. Increasingly, formal model property verification methods are also being applied to augment coverage. Upon evaluation of this coverage “dashboard”, the verification team lead can signoff for tapeout with high confidence.

To date, the verification of analog IP functionality to specification has typically been much less structured, with various ad hoc methods developed to assess the overall quality of the simulation strategy:

- specification documentation and testplan reviews

- schematic and layout reviews, with testcase simulation waveforms

- signoff documentation reviews

Just what every engineer looks forward to — more meetings. 🙁

Realistically, it is extremely difficult to apply metrics to reflect how the design of analog components and parasitics affect circuit behavior. Nevertheless, a more structured methodology for analog IP verification is definitely needed. This necessity is further advanced by the imposition of quality standard by various organizations, which define requirements for product release information — e.g., ISO 26262 for automotive market products.

To help address this issue, Cadence is announcing a major update to their popular Analog Design Environment (ADE) platform.

I had the opportunity to get a preview of the extensive verification features added to the new ADE product family from Steve Lewis, Product Marketing Director, Custom IC and Packaging Group.

Steve began by highlighting, “This is a new platform, consisting of ADE Explorer, Assembler, and Verifier. The focus is to enable advancements in analog verification methodologies. We will still be maintaining the existing ADE L/XL/GXL products — yet, we anticipate designers will eagerly want to adopt the capabilities of these new applications.”

The following figure illustrates the high-level focus of this announcement, using the ISO 26262 automotive quality standard as an example. The key bullet in this figure is“Traceability”.

Briefly, traceability implies that the product release must include documentation recording:

- what tests were run

- what environmental conditions were used

- the link between tests and design specifications

- what ran the tests, and when

- demonstrated success that the design specification was met by all related tests

Ad hoc verification methods to capturing and maintaining this information will not scale with the complexity of analog IP currently in development.

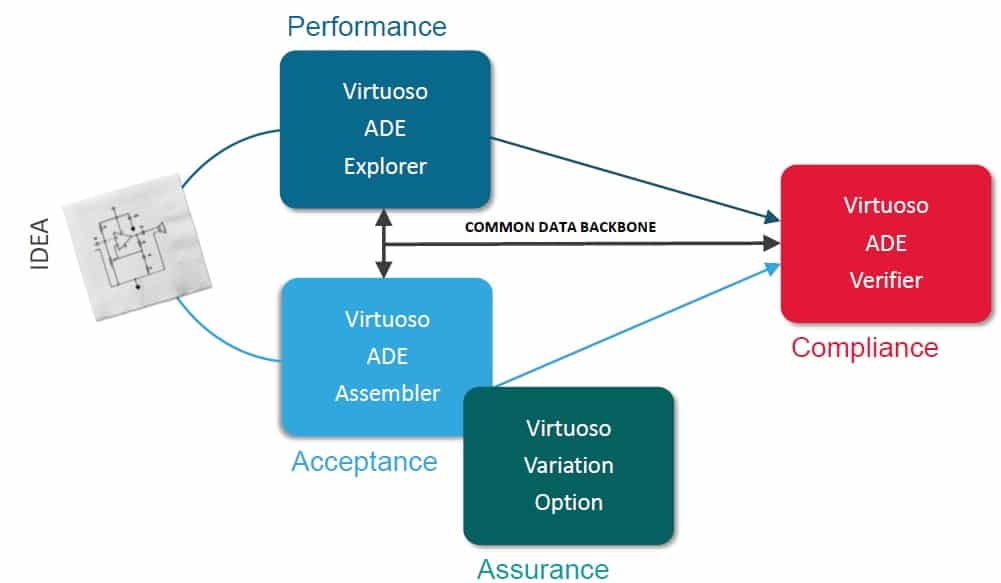

Steve described the new ADE products in some detail, using the diagram appended below:

ADE Explorer

Explorer is the day-to-day environment that the design engineer will typically use. Cadence re-allocated some capabilities from the existing ADE family into the base Explorer feature, recognizing that the advanced features of ADE L/XL/GXL are now de rigueur for all designers — e.g., Monte Carlo simulation support, sensitivity analysis.

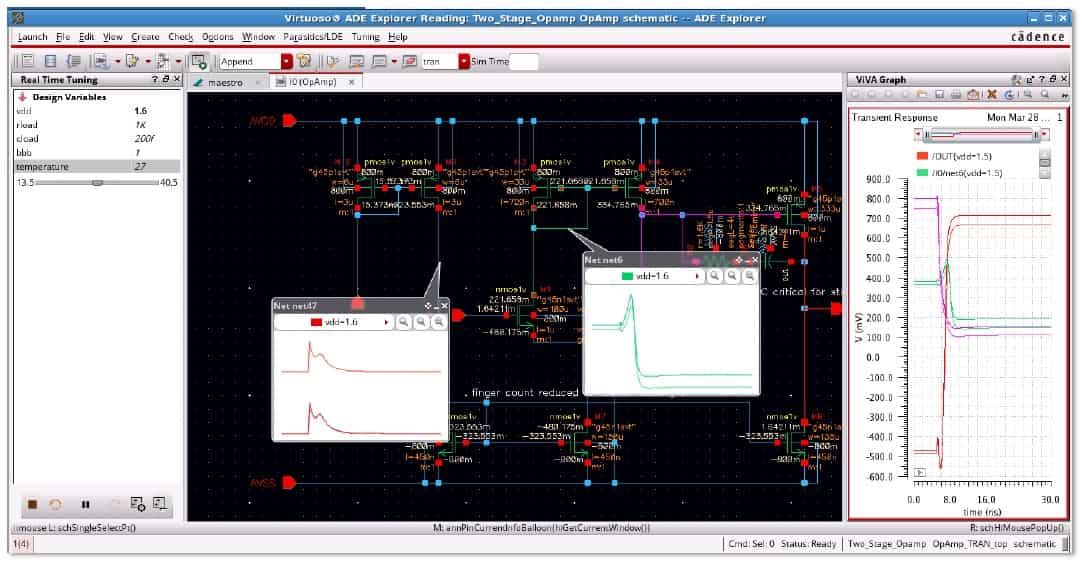

Significant usability features for faster iterative design closure were added, as well. For example, the figure below highlights thedesign tuning panel in Explorer, which facilitates rapid updates to schematic and environment parameters dispatched to Spectre or Virtuoso AMS Designer for simulation. Waveform balloons annotated to the schematic show comparative results, to more quickly iterate on design optimizations.

The key is that the simulation test results are maintained by Explorer in a model view used by ADE Assembler and Verifier.

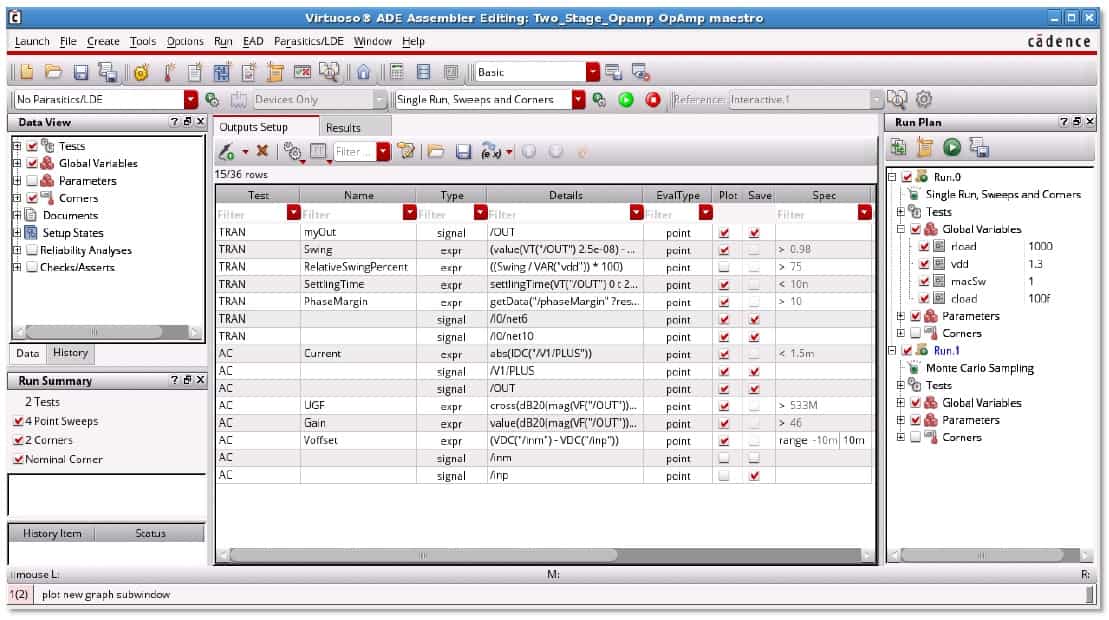

ADE Assembler

Steve associated the Assembler feature with prevalent use by the “block-level” verification team. Complex verification plans can be represented visually, as illustrated in the figure below. Conditional and interdependent testcase relationships (“run plans”) can be identified — for example, one set of test results are to be used in the next testbench set. Using the new ADE Variation feature, the verification team can apply high-sigma statistical, optimized Monte Carlo simulation tests.

ADE Verifier

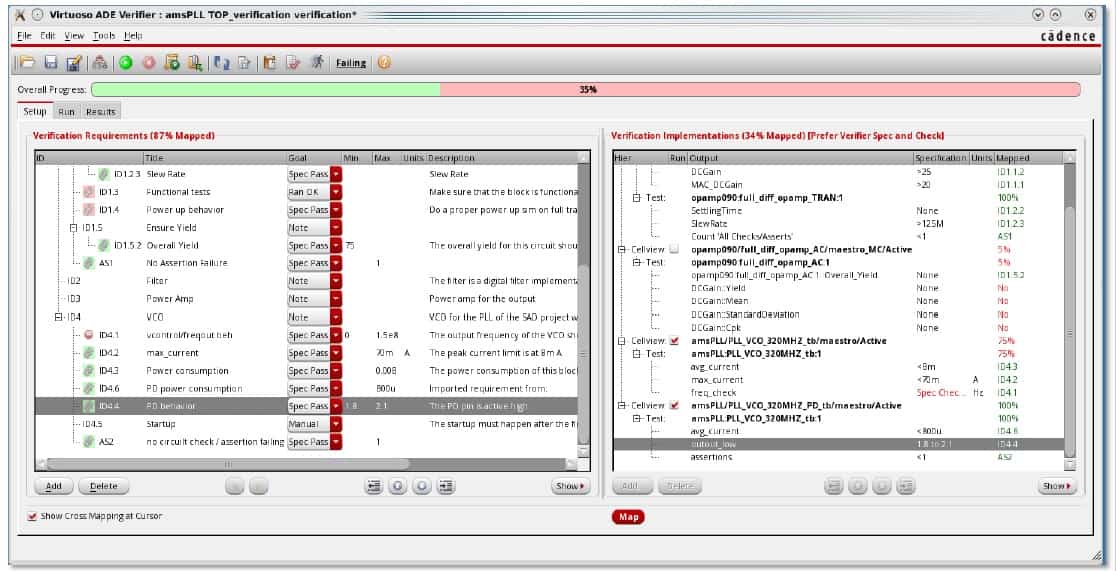

The verification plan originates and comes together with ADE Verified, an encompassing application that is used throughout the design cycle. Initially, as illustrated below, the correlation between design specification and testcase plan is established, a key facet to the traceability requirements of the product release standards.

During the design, Verifier provides the overall dashboard data that verification project managers will use, as depicted in the figure above.

As the design approaches signoff, Verification can also serve as the batch simulation regression test manager, as well.

Configuration Management

I asked Steve, “These ADE features look great, but they are clearly very dependent upon the configuration and version data management (DM) policies used during design. How is that handled?”

He replied,“Seamlessly. These new ADE features work directly with existing DM tools that ADE teams are using. These features utilize a new model view — maestro — that records and maintains all the traceability information required. The OA data model for the traditional Virtuoso views remains unchanged — e.g., schematic, layout, symbol views. The maestro view is added to the design database for the new Explorer/Assembler/Verifier features. We worked closely with the DM software tool providers to optimize the maestro view for performance. Existing ADE L/XL/GXL products are easily imported into the new ADE features, and the maestro view data accumulated.”

More robust analog IP verification methodologies are needed, to assist with increased IP complexity and the requirements for standards traceability. Yet, to gain rapid deployment, these approaches much be evolutionary, building upon existing tools and interfaces, providing usability features that are intuitive to analog designers and verification teams. With the new capabilities added to ADE — Explorer, Assembler, and Verifier — Cadence has enabled this rigorous transition to be quickly and easily adopted.

For more information on the new ADE product family, and the new Virtuoso product announcement, please follow this link.

-chipguy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.