Being engrossed in the digital information world, it is easy to forget that the real world is comprised of mostly analog signals and data. Digital Signal Processors (DSP) take digitized forms of these worldly signals and manipulate them mathematically. Although floating-point is a more relevant and accurate way of representing real world data, a significant volume of DSPs in deployment are fixed point DSPs. And these fixed-point DSPs have been meeting the needs of commercial applications well. Traditionally, floating-point computations have primarily been used in scientific applications.

Historically, the term floating-point has only received mainstream attention when bugs or errors have caused critical floating-point calculations to be performed incorrectly. Floating-point remained a topic of interest for only certain specialized applications until recently. It is not surprising that there are not many DSP cores optimized for floating point computations. Commercial, consumer and industrial market requirements are changing. As highlighted during executive keynotes at the CadenceLIVE Americas 2021 conference, today’s common applications are as complicated and demanding as “rocket science” applications. Floating-point DSPs have become imperative for today’s market needs. It is in this context that Cadence’s recent unveiling of their Tensilica FloatingPoint DSP family of products takes significance.

I had an opportunity to talk with Ted Chua, director of product marketing and management of Tensilica DSPs at Cadence. The following is a synthesis of what I gathered from our conversation.

Markets and Requirements

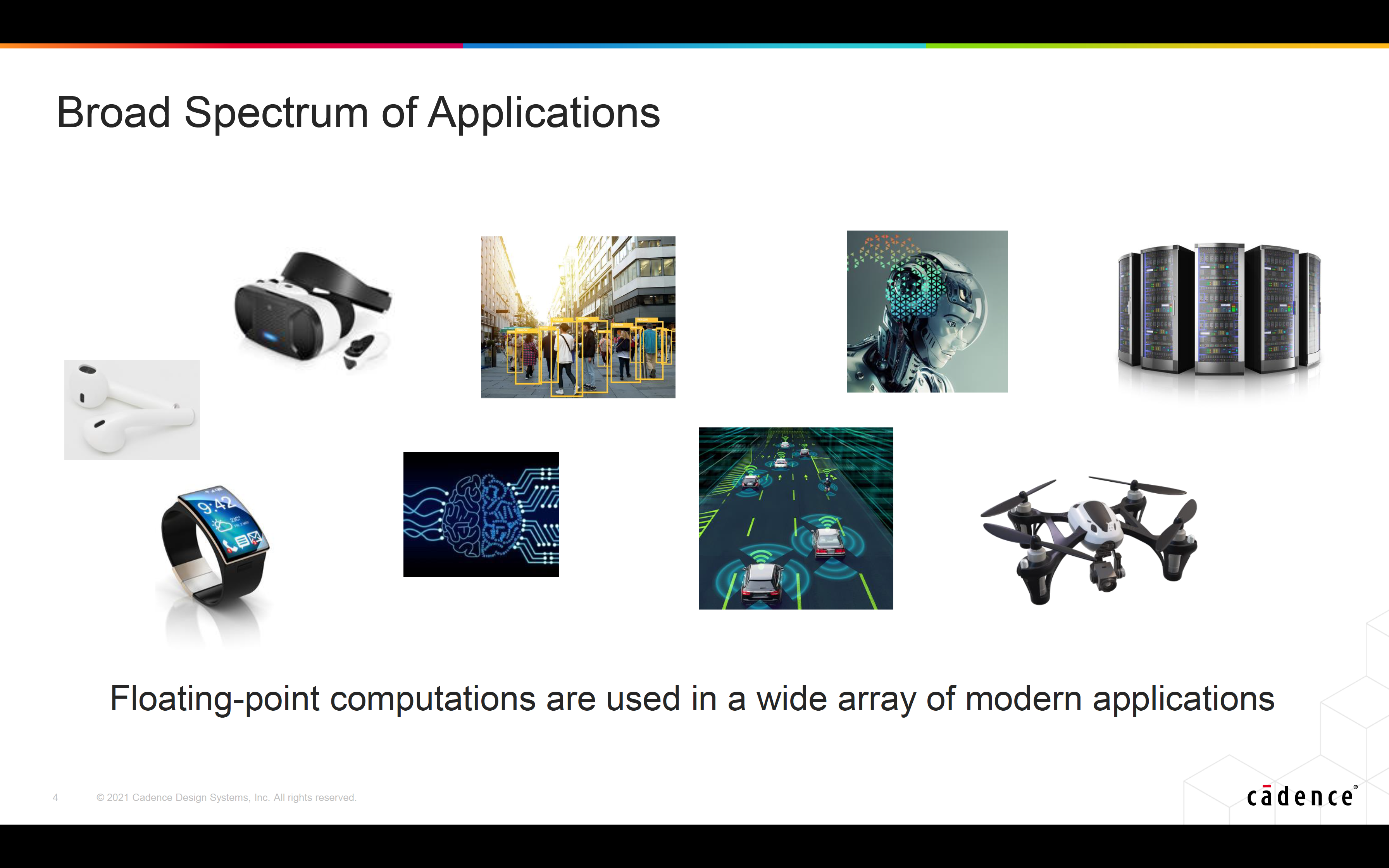

Applications that could benefit from floating-point DSPs range from energy-efficient solutions for battery-operated devices to artificial intelligence/machine learning (AI/ML), motor control, sensor fusion, object tracking and augmented reality/virtual reality (AR/VR) applications in the mobile, automotive, hyperscale computing and consumer markets. Many of these applications are fast evolving and moving from the cloud to the edge. What is needed is a family of floating-point DSP cores to address different market needs for quick time to market. The family must be designed for scalability with applications and supported with ease of configurability. The cores should allow for custom instructions for adapting to market trends. And these cores must be optimized for power, performance and silicon area to keep product costs competitive.

Cadence Tensilica FloatingPoint DSP Solutions

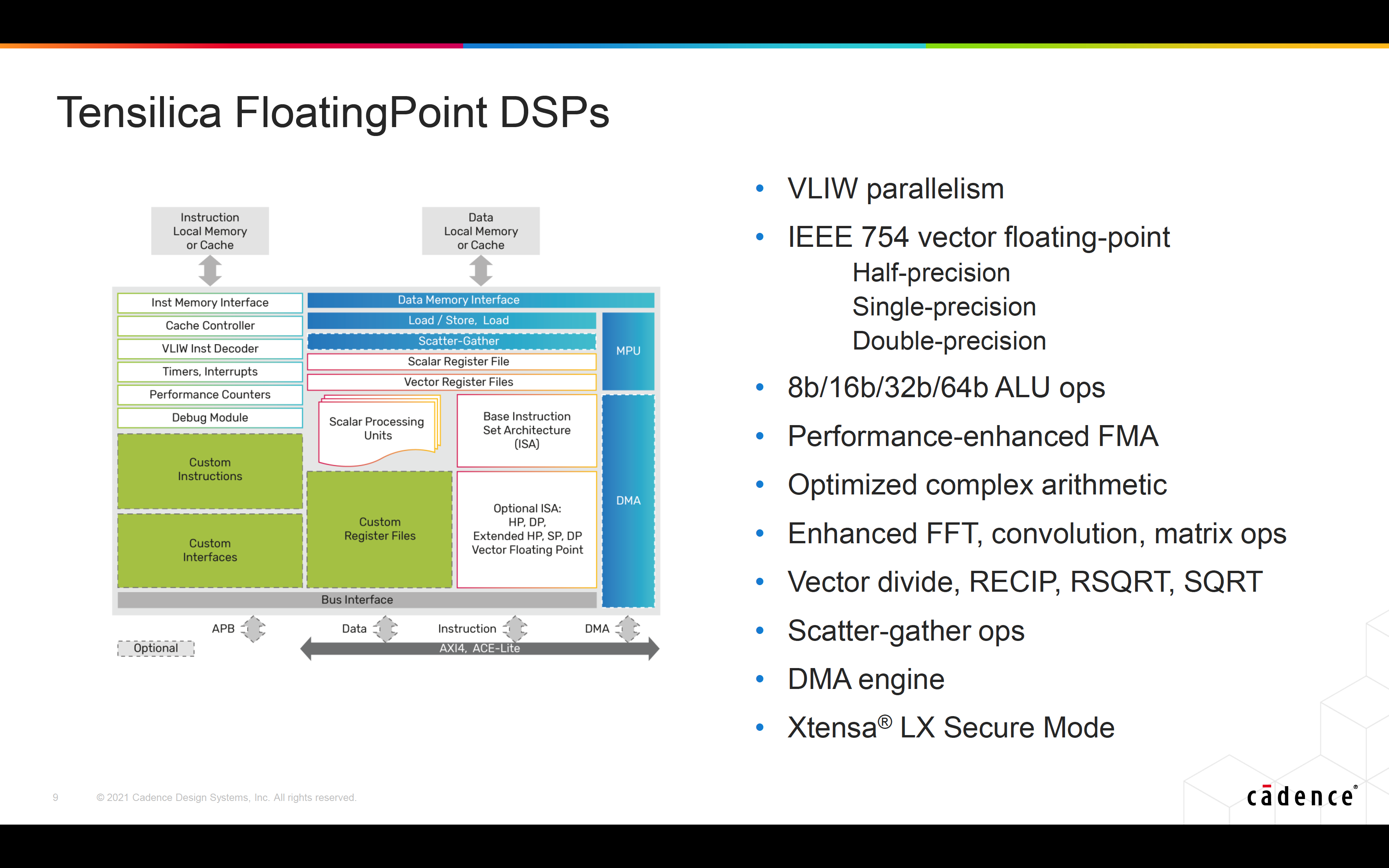

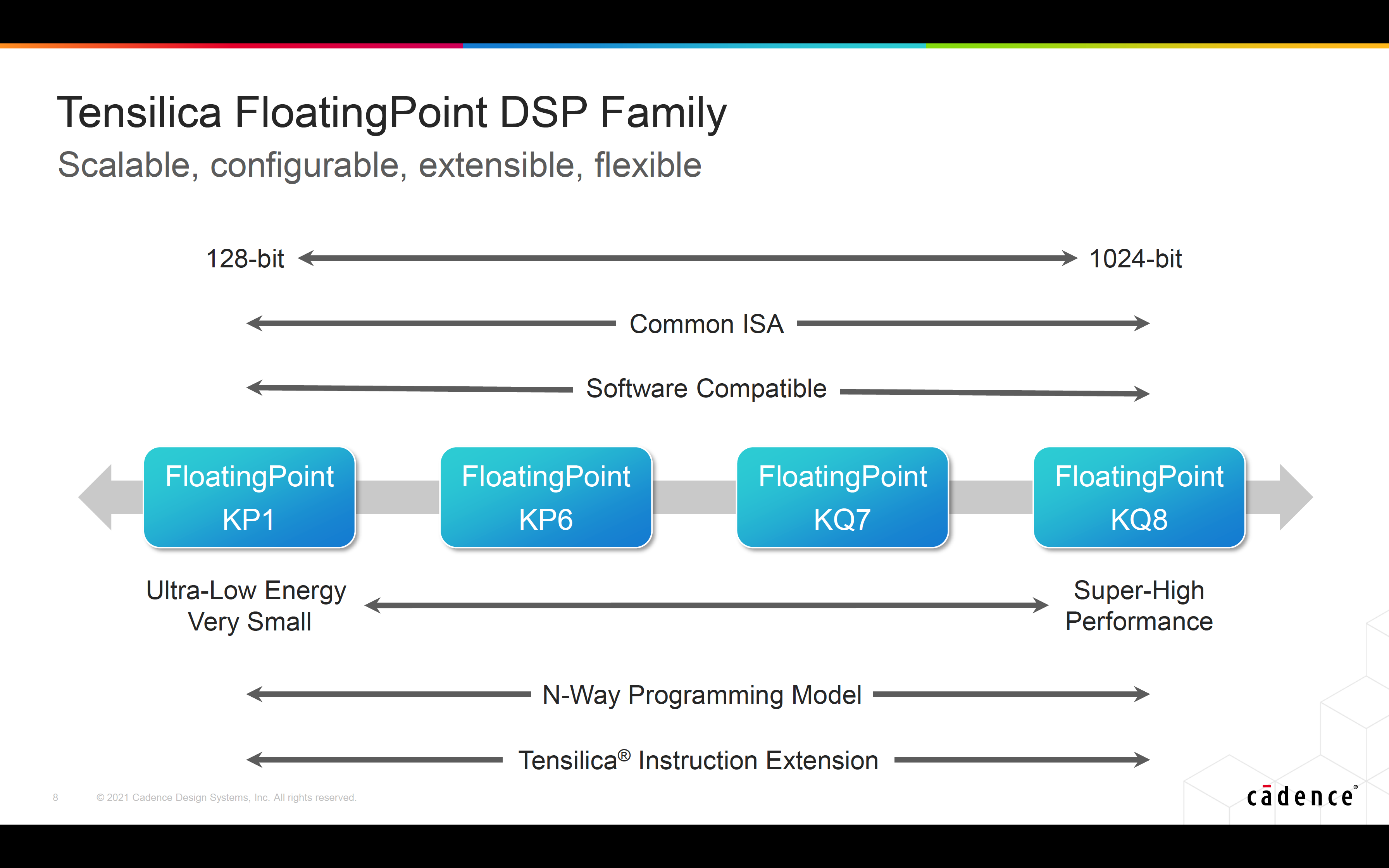

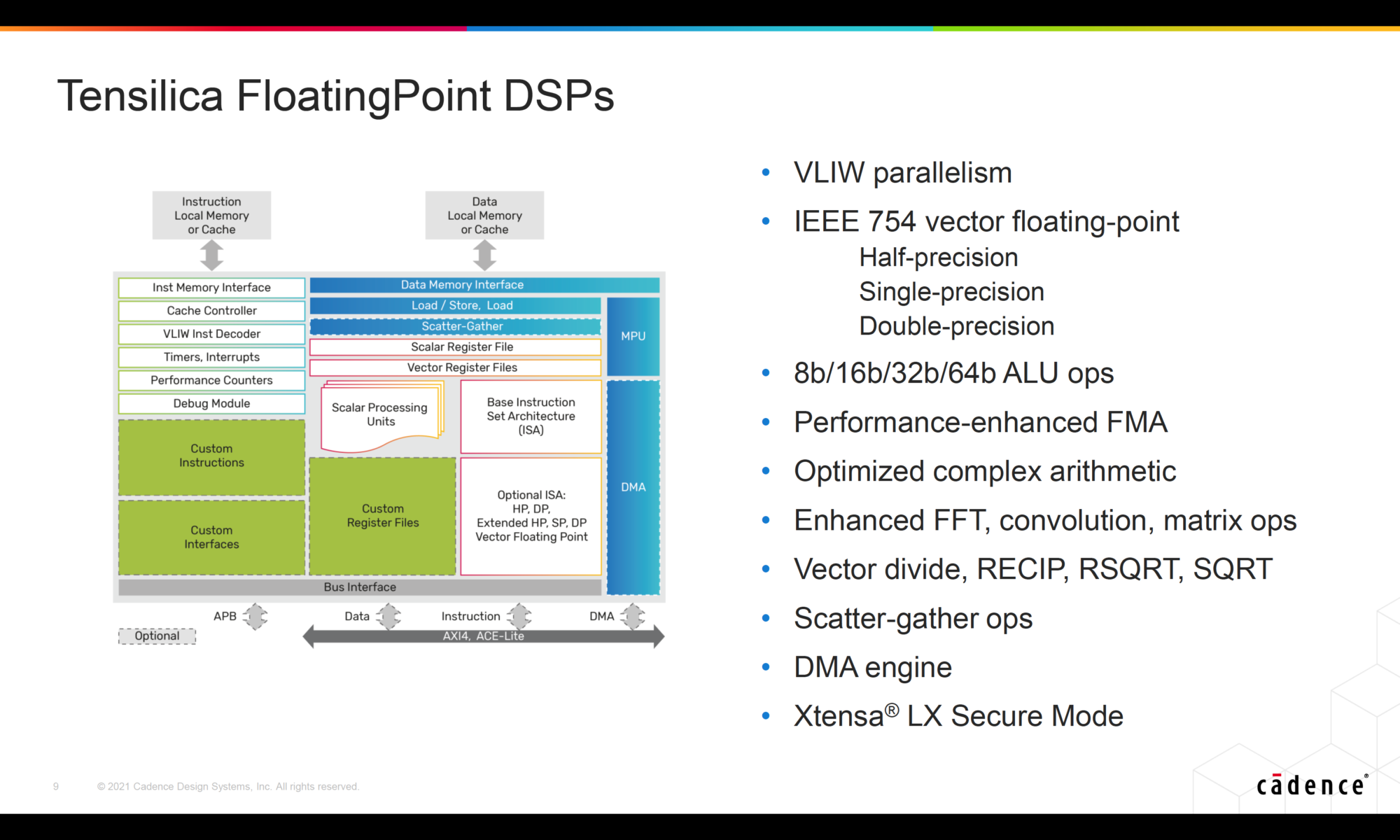

In general availability now, the family of products announced last month includes the Tensilica FloatingPoint KP1, KP6, KQ7 and KQ8 DSP cores. The products are built off of the widely used and well established Xtensa platform and ecosystem and support the Xtensa LX Secure Mode. The secure mode is a unique feature in a DSP core and enables customers to partition the memory into secure and non-secure regions and allow the protection of secure memory from untrusted third-party code. This feature permits inclusiveness of a broader selection of third-party codes without compromising on system security.

Refer to the figure below for some key features.

Scalable, Configurable and Extensible

Scalability– The DSP cores range from the ultra-low energy and very small 128-bit FloatingPoint KP1 DSP core to the super-high performance 1024-bit FloatingPoint KQ8 DSP core and are well-suited for a broad array of applications. Customers have the flexibility to choose the optimal cores for their respective application needs. Support for IEEE754 half-precision, single-precision and double-precision floating point is unique in the specialized floating-point DSP market today and further enhances the scalability of Cadence’s offering.

Configurability– The development platform makes it easy to configure to different SIMD widths by automatically selecting the vector packages without unnecessary hardware.

Extensibility– The Verilog-like Tensilica Instruction Extension (TIE) language allows customers to easily design and add custom instructions and custom interfaces to the DSP. It enables them to further enhance the performance and bring highly differentiated products to their customers.

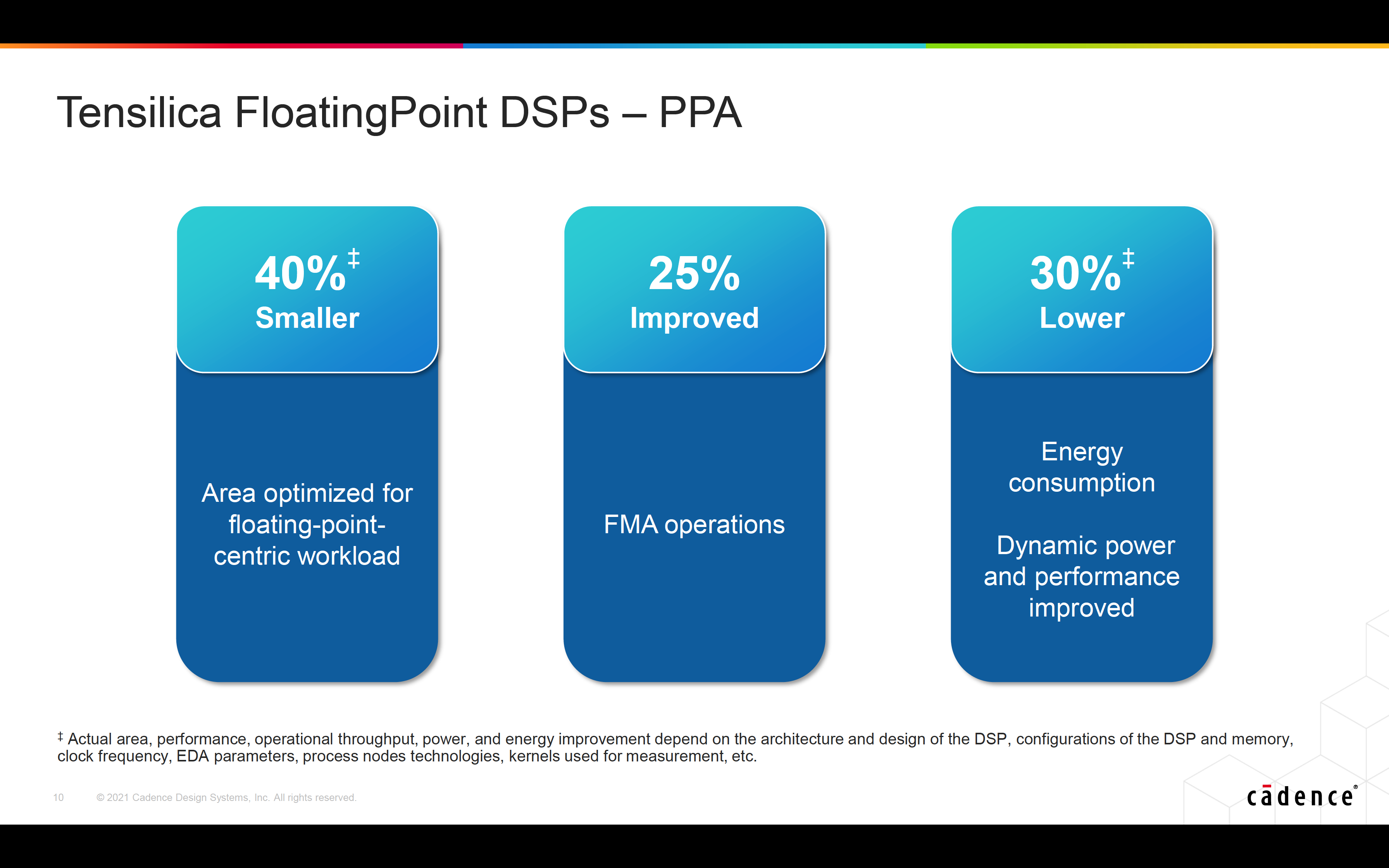

Performance, Power and Area (PPA)

The new DSP cores deliver a 25% performance improvement in fused multiply-add (FMA) operations compared to Tensilica’s fixed-point DSPs with vector floating point unit (VFPU) add-on. The TIE language not only allows for product differentiation but also enables further enhancement of performance of the product. The new DSP cores offer up to 40% silicon area savings compared to similar class of fixed-point DSPs with VFPU add-ons. Customers have the option to choose the optimal DSP core that fits their PPA budget for their application.

Overall, the optimized PPA benefits of the Tensilica FloatingPoint DSP family is a key value proposition for customers to bring differentiation to their respective customers. Refer to the figure below.

Ease of Development

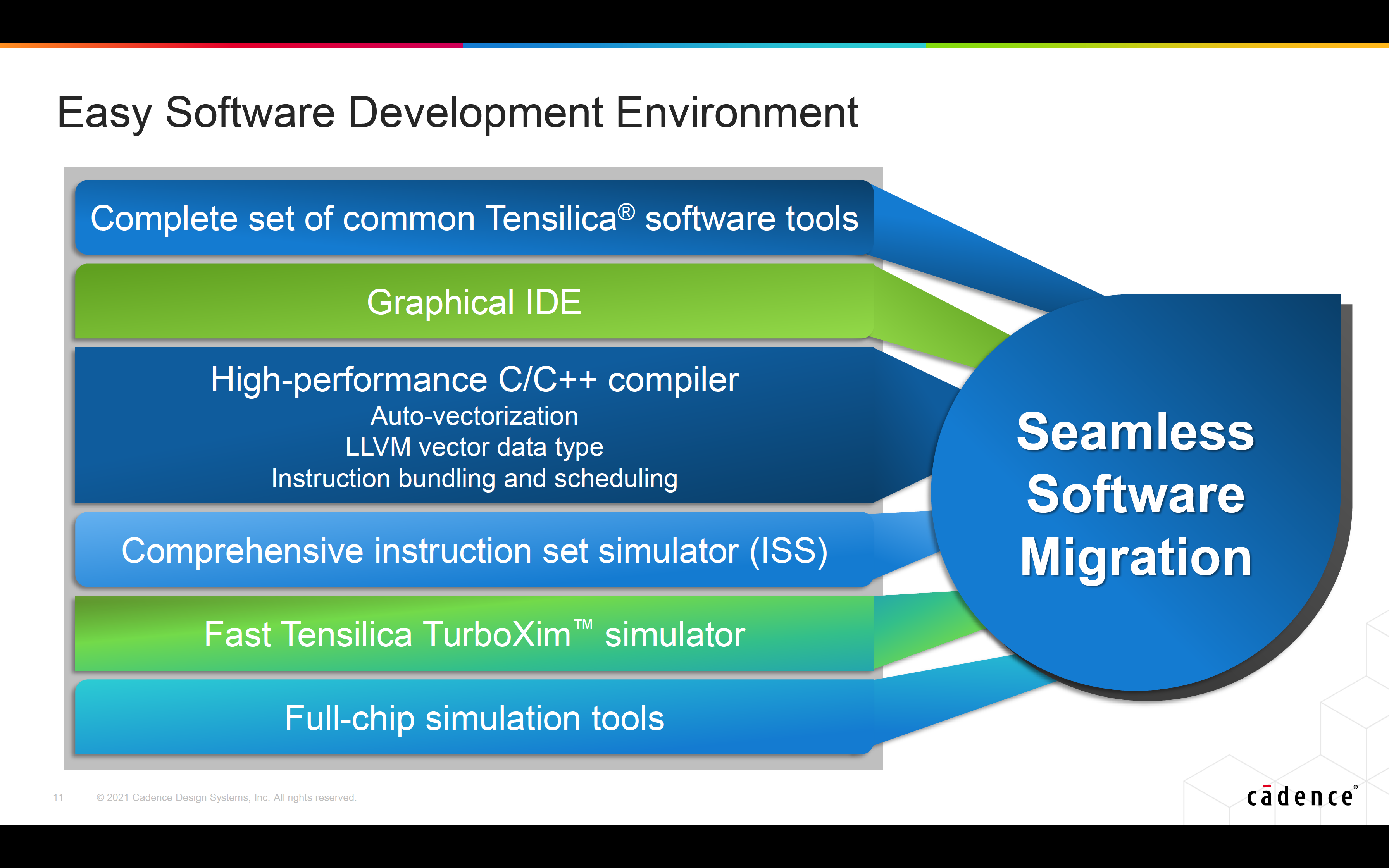

Ease of development is as important an aspect as the product features when it comes to bringing a solution to market ahead of competition. The development platform and productivity tools suite play a very important role in this aspect. Tensilica FloatingPoint DSPs are delivered with a complete set of software tools. This comprehensive toolset includes the linker, assembler, debugger, profiler, and graphical visualization. Refer to the figure below for more details. When working with large systems or lengthy test vectors, the Tensilica TurboXim™ simulator option achieves speeds that are 40X to 80X faster than the ISS.

The Tensilica FloatingPoint DSPs support all major back-end EDA flows. The optimized Eigen, NatureDSP, simultaneous localization and mapping (SLAM) and math software libraries enable easier migration of customers’ software to fully leverage the FloatingPoint DSPs.

Summary

The Tensilica FloatingPoint DSP Cores address the higher-precision data representation-format need as well as the scalability, configurability, extensibility and PPA requirements of modern commercial, consumer and industrial applications. The press announcement can be found here and more details can be accessed here at the Product section of Cadence website. If you are developing products for any of these (refer to the above figure) high-growth, fast changing markets, you may want to explore ways to benefit from Cadence’s recently introduced Tensilica FloatingPoint DSP cores.

Also Read:

Features of Short-Reach Interface IP Design

112G/56G SerDes – Select the Right PAM4 SerDes for Your Application

Lip-Bu Hyperscaler Cast Kicks off CadenceLIVE

Share this post via:

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea