High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating signals. One must pay attention to traces going from one layer to the next and to return current flowing on one power plane, when return current has to jump to another plane somehow. The challenges include PI, SI, return path analysis, EM modeling and an understanding of metal and dielectric structure. HyperLynx solves those challenges.

A vast bulk of designers do not know how to do this high-speed analysis, getting to a point where experts are needed. Todd Westerhoff, HyperLynx product manager, calls it the ‘expert bottleneck’ during a chat at DesignCon 2019. He states “With signal integrity design challenges, it is harder to find the expert and the time. HyperLynx relieves the need to have a dedicated SI person. Point tools offer the best in this and that. HyperLynx brings all this together. If you are designing a 112G device and wondering how to perform the complex analysis, with a signal out of one device on board, through a via and off, you will look at each part of the signal hierarchy. How does the field behave? You do not decompose at all and put into an electromagnetic solver, as this is too big of a problem. You can section it, and bring it back together. Can you do a distributed analysis? You can look at a whole path and break the trace into different segments and make it a 2D problem, but when you go through a via and board coupling, it becomes a 3D problem. The current next to a via becomes irregular. Far enough from a via, you get a constant cross-section and solve through the disruption. This is not complicated, it is standard housekeeping, but it becomes difficult not to make mistakes. HyperLynx takes care of that.”

When modeling interconnect, you bring the board database from the CAD system, the tool looks at the layout, and finds where the nets are. EM analysis produces S-parameters. Once the channel is modeled, the simulators become simulator specific but are still agnostic on the data format.

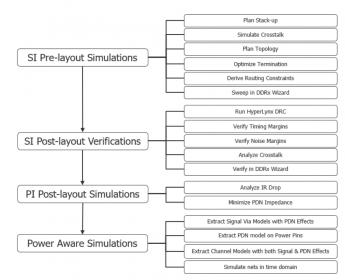

HyperLynx is a suite of tools which include signal integrity (SI), power integrity (PI), an electromagnetic (EM) solver, a DRC expert rule-based checker for problems like thermal issues. In rules-based geometry checking (DRC), the checks return currents in terms of signal propagation. Usually, PCB designers manually review the database and sometimes they eyeball the layout and turn on traces. The problem is that it is easy to miss something. Pattern-based, DRC geometry checking extended to many levels, EM modeling, simulation, and modeling technology are needed. The goal is reading the layout and checking for common problems without modeling all the IO. There are limited ways to do what-ifs and doing an incremental analysis. Some items to note:

● There is a pre and a post route signal integrity analysis distinction: Pre-route is what-if, post-route is verification and validation.

● All tool modules are integrated so patch releases are in one release.

● HyperLynx is leading in making simulation easy to use while preventing costly repairs.

● One can open HyperLynx from within Xpedition. HyperLynx has the ability to create reports for certification including electrical safety compliance.

● There is a big gap between how many SI and PI experts are needed and how many are available. With the pervasive expert bottleneck, the problem is getting worse, thus the need to take sophisticated analysis to a broader audience. Managing expert availability is always a challenge. Using the analogy of vinyl records, Westerhoff quips ‘you want the needle to stay on the record, but it keeps skipping’.

Reducing Certification Risks

One of the increasing challenges for system, board and chip designs is comprehensive automated design checking and verification while meeting the increasingly demanding certification requirements. Manually verifying a schematic, layout and prepping for manufacturing is time-consuming. IEC safety standards need to be met and power and signal integrity issues need to be addressed in a timely fashion.

These verification tools work in any flow and can be sold standalone. However, their integration with Mentor’s Xpedition flow has an advantage. This allows the person performing the schematic capture or layout design the ability to fix the errors without the usual back and forth of simulation and without adopting a new tool.

Automated Design Compliance Testing with Xpedition Validate features include:

● Fully automated proven schematic integrity tool designed to replace visual inspection

● Exhaustive power and technology aware test of all schematic nets

● Parametric error detection

● Warnings highlighting poor design

● Major EDA tools agnostic

● No additional infrastructure required

● 150+ automated checks

● 6+ million library parts

Examples of checks performed include:

● Open collector/drain

● Poor practices (lack of needed pull-ups/pulldowns)

● Power/ground connectivity

● Component power checks

● Multiple or missing power supplies

● Differential pin checks

● Unconnected nets or buses

● Off-board net collection

● Overloaded pins

● Unconnected mandatory pins

● Nets missing driver

● Diode orientation

HyperLynx Scalable High-Speed System Design

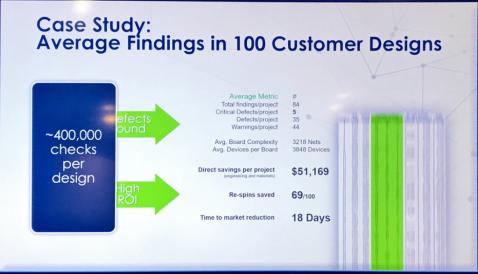

A study of 100 customer designs showed that direct savings exceeded $51K per project and of those 100 designs, 69 were spared a re-spin with 18 time-to-market days reduction.

● After models are assigned, the designer can scan for voltages on the nets or export from CSV format.

● The IEC standards are embedded in the rules.

● Automatic checks such as output threshold can be run.

● Power net checks decoupling caps detection, return path reference point changes.

● HyperLynx DRC can be run inside layout, can check 3D, multilayer creepage, a big safety issue.

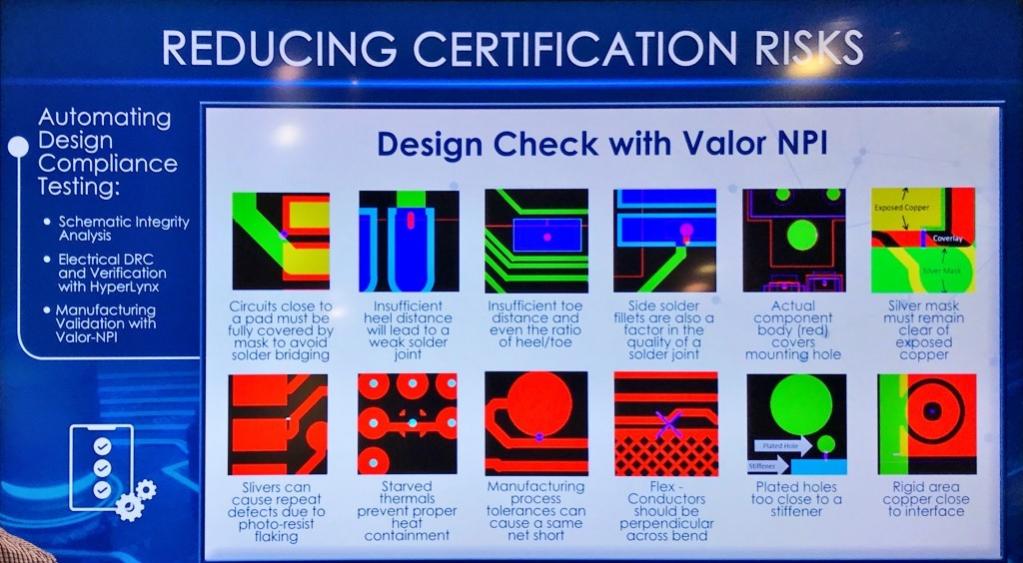

● Automating manufacturing Valor does those checks, allowing a move from proto to production.

● Will check weak solder joints, flex conductive materials, manufacturing issues.

● Valor includes 35 million industry standard manufacturing part numbers and will do a virtual prototype of the build. Valor can also be run inside the layout tool. If constraints are changed, Valor will read these changes dynamically and update.

● Automated compliance checking for schematic, layout and manufacturing.

Physical Design Checks Certification Risk Reduction with Valor NPI

HyperLynx Model-Free Analysis Flow

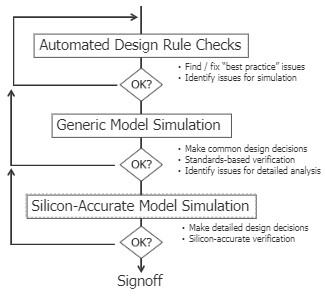

An automated Design Rule Check finds and fixes marginal and questionable practices and identifies simulation issues before embarking on a detailed analysis which checks common design decisions and applies standards-based verification followed by silicon-accurate verification that would allow signoff. This simple screening for errors and the use of protocol models minimizes expensive vendor-specific simulation and lengthy runs.

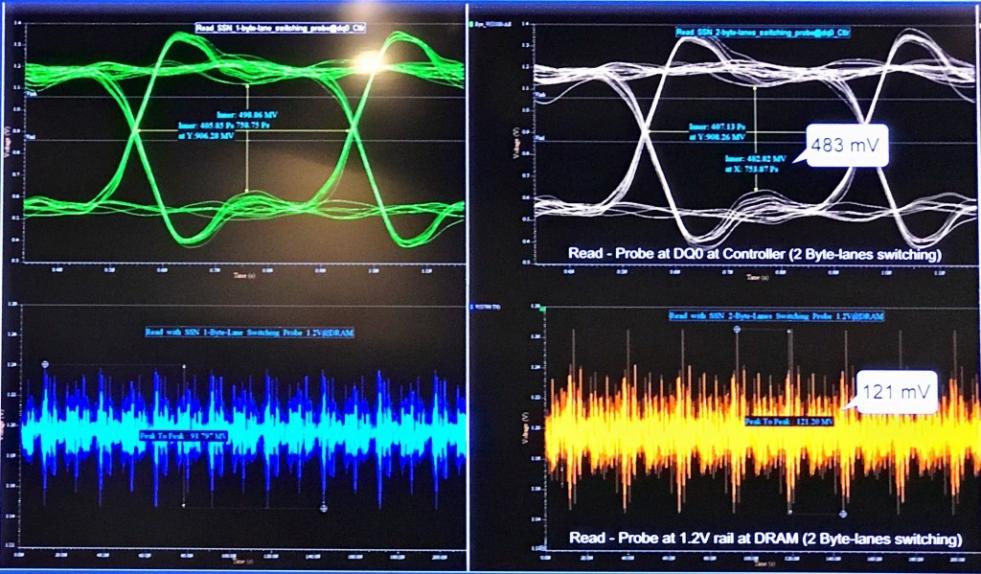

The power-aware simulation includes 3 separate types of Signal Power Distribution network (PDN) interactions:

● Multiple driver switching and power supply effects

● Via-to-via coupling through PDN cavity

● Non-ideal trace return path effects.

This power-aware simulation reduces overdesign and reliance on guidelines that may add design cost and complexity. Another benefit of power-aware simulation is the ability to make design tradeoffs for high-volume, low-cost, layer and space constrained designs.

Power-Aware: HyperLynx DDRx Design Flow

With the ability for the designers to do their own validation, the experts are freed up to focus on more complex multi-physics analysis for specific tough problems. This best practice allows shortened design cycles, reduced re-spins and higher product quality with errors caught early in the design cycle.

Mentor automated design compliance testing tools reduce certification risk with shorter turnaround time due to the following:

● Automated tools from Mentor allow every net, component, or scenario in a design to be checked, and are not just limited to critical areas the designer has time to check

● These tools work in any flow and can be sold standalone. However, their integration with Mentor’s Xpedition flow provides an advantage. This allows the person performing the schematic capture or layout design the ability to fix the errors without the usual back and forth of simulation and without adopting a new tool since the compliance testing works with current Xpedition GUIs and Xpedition format

● Certifications issues are identified in real-time, not at the end of the design cycle.

HyperLynx and Xpedition flow allow model-free analysis, power-aware simulation well suited for high-speed design, ensuring reliability, safety compliance with reduced cycle-times and certification risk in a cost-effective way.

[More information on HyperLynx]

Comments

There are no comments yet.

You must register or log in to view/post comments.