In conjunction with the 2018 International Test Conference, Mentor has several interesting test announcements. They also have a busy round of technical activities, including a number of technical papers, presentations, tutorials and a poster from a major customer about using Mentor. I’d like to touch on the two product related announcements, because they are pretty interesting.

There is probably no area other than automotive where reliability has received more focus lately. First off, zero defects are a prerequisite for ISO 26262. Also, the automotive semiconductor market is experiencing higher growth rates than almost any other sector. As such, automotive applications have become the reference for quality and reliability. It is pushing the development of improved methodologies and is setting the standard for the highest reliability.

Automotive is on a steep complexity growth curve, both historically and for the immediate future. It used to be that automotive semiconductors could leisurely stay behind the bleeding edge of technology. However, ADAS and new requirements for infotainment have brought automotive computing and data transfer requirements to the point where only the most advanced nodes will suffice. Going from Level 2 to Level 4/5 for ADAS will increase the number of sensor modules by around a factor of 5. Higher levels of automation will require more complex computational tasks. For example, AI algorithms may be used to anticipate pedestrian movements to help avoid auto versus pedestrian conflicts. All of this adds up to more complex chips and more of them, which will necessitate increased effort to ensure the highest reliability.

To address the needs of this market Mentor has added a new set of test patterns to deal with failure modes found in FinFET processes and 3D transistor structures. Mentor Tessent TestKompress already looks at each cell to determine areas that are vulnerable to defects. Now they are adding analysis that will look at cell to cell interactions looking for potential defect sources. Several Tessent customer are publicly reporting significant reductions in their DPPMs, in the ranger of 700 to 4300, by using the improved analyses offered in Mentor’s automotive-grade ATPG.

With the added automotive-grade test patterns it should be possible to replace many system level or functional test patterns. Mentor has added automated pattern generation that targets critical-area based interconnect bridges and opens, as well as cell internal and neighborhood defects.

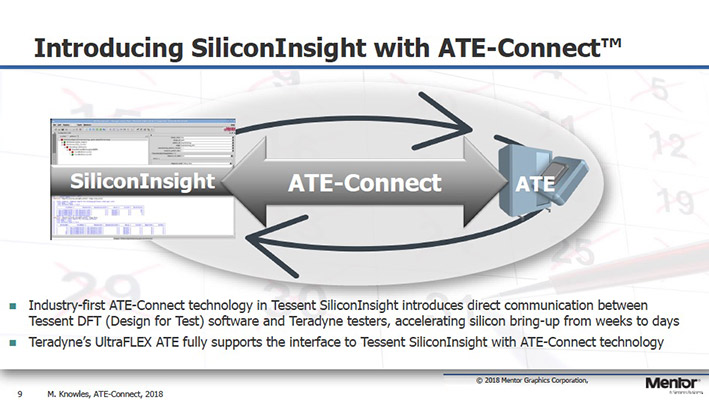

Mentor’s other announcement concerns improving the efficiency of silicon bring-up. Mentor has created a networked connection between the DFT software and the testers themselves. They worked with Teradyne to interface UltraFLEX ATE to Tessent SiliconInsight. Because literally hundreds of IP blocks are being added into new SOC designs, IJTAG has seen strong adoption. With this comes the need for IJTAG debug tools. With the introduction of Mentor’s Interactive IJTAG, designers can get better insight into what is happening on the tester, right in their test software in real-time. Reduced iteration time can shorten bring-up from weeks to days. Interactive IJTAG speeds up the many complex mappings that are needed to generate the test program on the tester and then interpret the test results in a way that is meaningful to the designer.

The 2018 ITC features papers from Tessent customers discussing real world results with TestKompress Automotive-grade ATPG and SiliconInsight Interactive IJTAG. Mentor is vigorously involved in improving the state of the art in test. This shows in their ISO 26262 qualification for use on all ASIL ISO 26262 projects. System designers and end customers are the beneficiaries of their sustained efforts in test. There are more details on these new announcements and Mentor Test products on their website under TestKompress or SiliconInsight.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.