The 46[SUP]th[/SUP] IEEE International Test Conference (ITC) will be held the week of October 5, 2015 at the Disneyland Hotel Conference Center in Anaheim, California. ITC is where you will discover the latest ideas and learn about practical applications of test technologies.

The 46[SUP]th[/SUP] IEEE International Test Conference (ITC) will be held the week of October 5, 2015 at the Disneyland Hotel Conference Center in Anaheim, California. ITC is where you will discover the latest ideas and learn about practical applications of test technologies.

As you take in panels, tutorials, presentations, and the exhibits, you might find that some common themes emerge as the folks in the world of test grapple with finding solutions to today’s biggest issues. I talked with Ron Press, Technical Marketing Director of Tessent Solutions at Mentor Graphics, and Vice General Chair of the ITC Steering Committee about the trends he sees that are testing the limits of test technologies.

According to Ron, “We see two growing trends that people are trying to resolve. The first issue is how to provide efficient test methodologies when dealing with giga-gate designs. The other issue is how to manage pattern-set sizes in these huge designs as well as supporting designs with additional patterns, such as cell-aware, in order to meet quality requirements.”

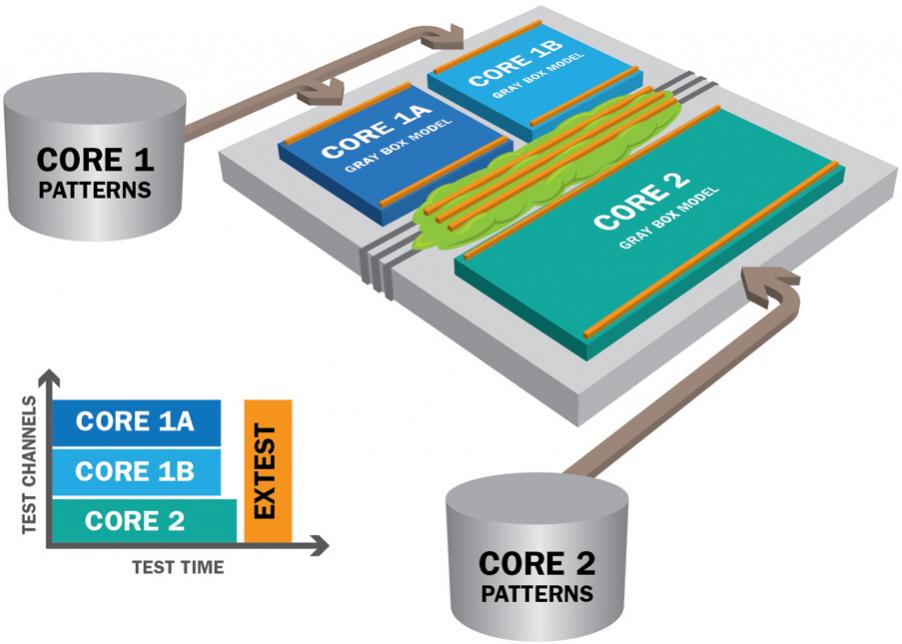

To address the deployment of giga-gate testing, Ron said, “Hierarchical test is beneficial for designs with 20 million gates and often viewed as required for designs over 40 million gates.” Divide and conquer has been the methodology employed for all phases of enormous chip design and design-for-test (DFT) now joins that practice. Using hierarchical test, the DFT features and test patterns are completed on individual blocks and then reused at the top level.

Teams bringing hierarchical test to bear on big designs are looking to achieve these goals:

- Move up DFT insertion and pattern generation earlier in the design process

- Reuse block-level patterns

- Allow geographically-dispersed teams to work on individual blocks without needing the top-level design

- Enable automatic test pattern generation (ATPG) to be performed on smaller workstations

- Significantly reduce test time and ATPG run time

It is a myth that top-level pattern generation for the entire chip in one ATPG run is more efficient for test time versus testing blocks individually. Actually, hierarchical test is often 2-3x more efficient than top-level test. Annapurna Labs is presenting a conference paper on their hierarchical test methodology. Spreadtrum Communications and Mediatek will be discussing their successful use of hierarchical test techniques in the Mentor Graphics Theater.

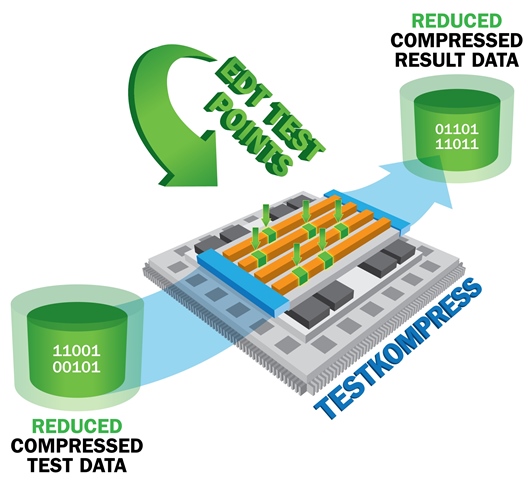

Huge designs fuel the growth of scan pattern-set sizes. Ron said, “A new approach is necessary to greatly improve the ability to efficiently test designs with large pattern sets. This approach applies a new type of test point identification to embedded deterministic test (EDT). We have seen a 2x-4x reduction in test-pattern count using this new approach.”

Huge designs fuel the growth of scan pattern-set sizes. Ron said, “A new approach is necessary to greatly improve the ability to efficiently test designs with large pattern sets. This approach applies a new type of test point identification to embedded deterministic test (EDT). We have seen a 2x-4x reduction in test-pattern count using this new approach.”

With the growing use of cell-aware patterns, test teams see bigger demands on test time. That is why there is growing interest in the new EDT test point solution. For example, Intel is presenting a paper at the conference that relates their success in using EDT points for compact, cell-aware tests. In the Mentor Graphics Theater, Broadcom will be discussing real-life data on their experience using EDT points.

If you are heading to Disneyland for ITC, be sure to attend the hierarchical giga-gate testing and managing pattern-set size sessions. Drop by the Mentor Graphics Theater to hear real world applications of these solutions. And, introduce yourself to Ron Press. He is always happy to talk about test.

Comments

There are no comments yet.

You must register or log in to view/post comments.