AI technology was prevalent at DAC 2025, but can we really trust what Generative AI (GenAI) is producing? Vishal Moondhra, VP of Solutions Engineering from Perforce talked about this topic in the Exhibitor Forum on Monday, so I got a front row seat to learn more.

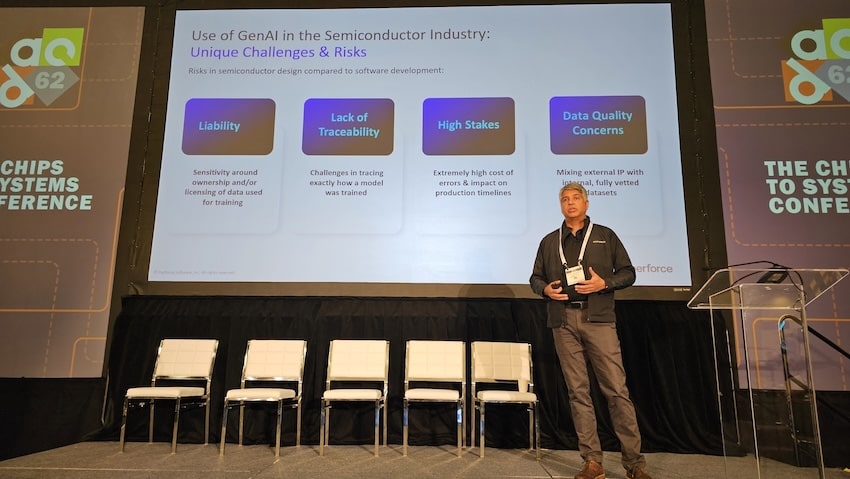

Vishal started out by introducing the four challenges and risks of using GenAI for semiconductor design:

Liability questions arise over who owns the IP in a new design, how the IP is being licensed, and whose data is being used to train an AI model. Companies need to know how AI models were trained, so that training is a traceable procedure. What if a new IP block was created by GenAI and it contains an error, lengthening the time to production and increasing development costs? When mixing both external IP with internal IP, are there data quality concerns?

Establishing trust for using AI to train models requires three pillars:

- Clear and auditable data provenance for all training datasets

- Complete traceability of IPs and IP versions

- Secure and compliant use of both internal and external IP

With the Perforce methodology, a semiconductor team will use IP lifecycle management to provide the proper provenance for training datasets. Team members define their design in terms of IPs, establishing provenance for each IP, providing complete traceability down to the file level, along with its history. Data contamination of the dataset is avoided by adding and enforcing rules about IP usage. Incremental training is supported, giving users a history of what changed since the last training set. All of this reduces the risk of using GenAI to train models for semiconductor design.

Vishal spoke about what an IP object could be: processor, memory, register, library cell, PDK, chiplet, embedded SW, or firmware. Adding metadata to an IP block enables permissions to be set, technical specs to be added, properties to be defined, usage set, versions updated, and even bugs to be tracked. IP lifecycle management enables high-level abstract IPs to have dependencies, form subsystems and use hierarchy. Even the environment configuration is stored as workspace settings, documentation, startup files and scripts, or templates.

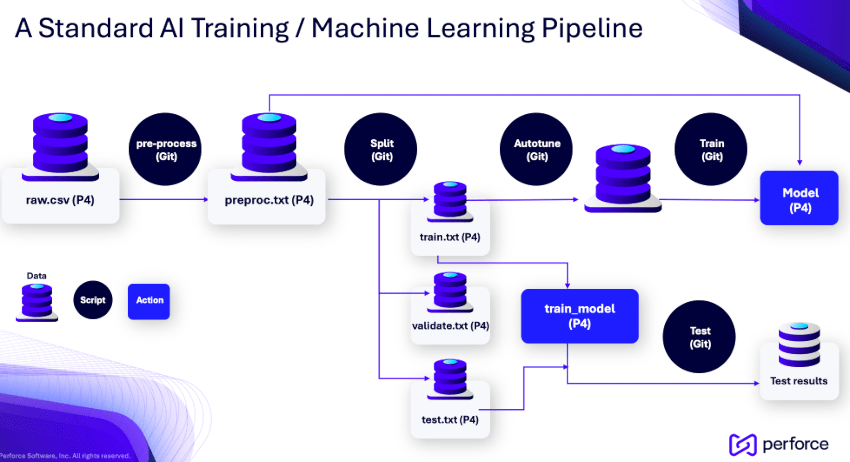

The AI training process was presented, showing the flow of how files are created and models formed by using scripts and actions. With Perforce, a completely traceable flow of data creates new training data, and the pipeline can be run multiple times.

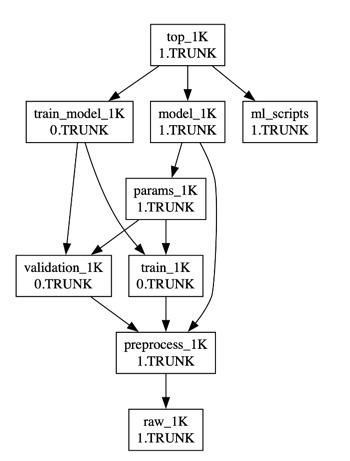

With an IP Lifecycle Management (IPLM) flow, all data sources can be modeled as IPs. Each derived data source becomes the parent of the source, and the preprocessed data is the parent of raw data, while training data is the parent of the preprocessed data. Both the training and final models are also modeled as IPs. Each script that runs a data transformation and model training becomes an IP.

Using IPLM in AI/ML training pipelines allows semiconductor teams to manage all of their data and dependencies, creating a series of parent-child relationships. Data management can be mixed between tools like Perforce P4 and Git based on user preferences. Teams can quickly build new workspaces with the right data, scripts, and models each time. This whole ecosystem is fully traceable, so you always record the data source, know how the derivatives were assembled, have a record of all parameters, and ensure that all models are fully traceable and reproducible. Engineers learn how to add metadata to the training projects, like the training parameters, results, history of runs and runtimes. You can view and model the model lineage to see which project was derived or copied, and where it came from.

Summary

GenAI is sweeping across the EDA and IP landscape, so it’s worth questioning the integrity of this new paradigm. The software team at Perforce has thought about each trust challenge and come up with an approach to make GenAI model development and usage trustworthy. Learn more about Perforce and semiconductor design by visiting their website.

Related Blogs

- Perforce at the 2025 Design Automation Conference #62DAC

- Video EP1: A Discussion of Meeting the Challenges to Implement Gen AI in Semiconductor Design with Vishal Moondhra

- Perforce IP and Design Data Management #61DAC

- Perforce at the 2024 Design Automation Conference

Comments

There are no comments yet.

You must register or log in to view/post comments.