Custom and analog/mixed-signal IC designs have some unique IP and symmetry checking requirements for physical design. Waiting until the end of the IC layout process to verify IP instances for correctness or proper symmetry will cause project delays, so an approach to perform earlier physical verification makes more sense. I’ll share what I learned from reading a recent technical paper from Siemens on the Calibre Pattern Matching tool.

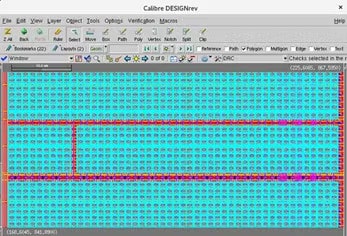

IP reuse is common for SoC design, but what if your IP block has a placement error like the one shown below in a memory cell array?

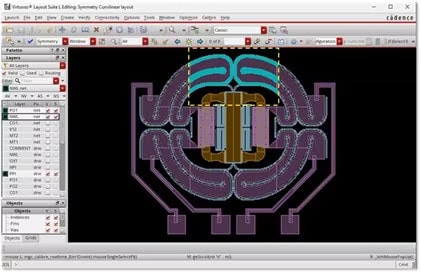

Symmetry of layout for many analog and mixed-signal designs is critical to achieve the specifications and for reliable operation. Doing manual symmetry checking with measurement tools is a slow and error-prone process. Applying cell mirroring or cloning are great design techniques but still needs to be validated. Circuit symmetry requirements could necessitate that new rule checks be created and may take too much development time.

Calibre Pattern Matching

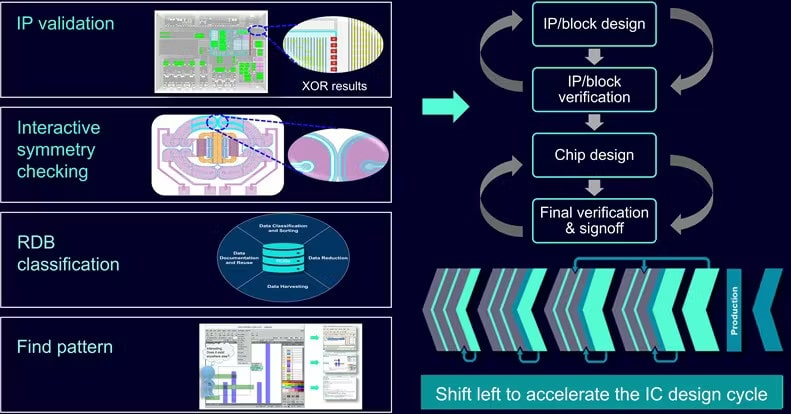

There’s a tool from Siemens called Calibre Pattern Matching with new capabilities designed for early-stage physical verification of layout. Here’s the flow for when to run the tool.

Layout engineers can now verify layout symmetry interactively, saving time by using Calibre Pattern Matching with Calibre RealTime, all without coding specialized rules or resorting to measuring manually. Here’s what interactive symmetry checking looks like in the Cadence Virtuoso layout editor.

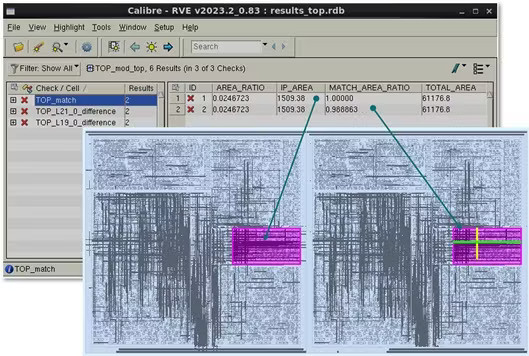

When an IP block is instantiated in a layout the placement or alignment issues can be automatically caught with Calibre Pattern Matching, as shown next where two IP instances are verified and one is a 100% match, but the second instance has, what looks like, two metal routes crossing over it resulting in two XOR differences.

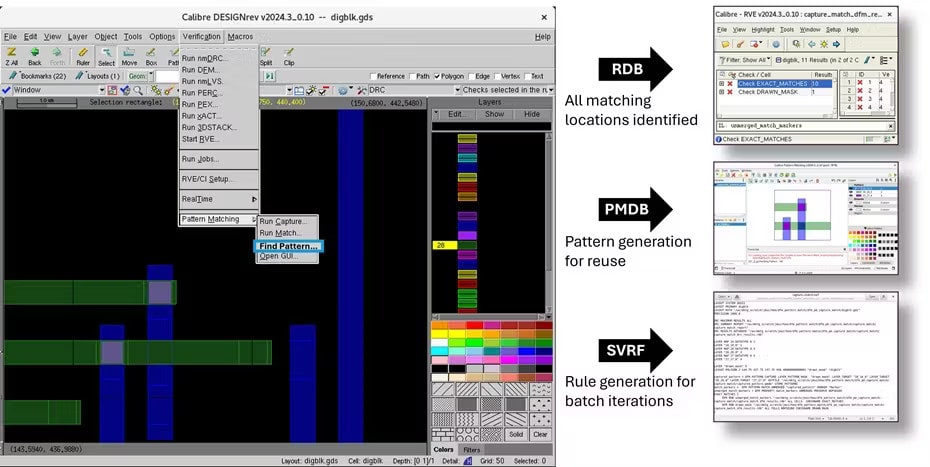

Your layout designers can ensure that critical IP blocks are placed consistently and verified early in the design. To find a particular layout pattern through a project, the designer can use the “Find Pattern” feature by selecting a layout area, then the Calibre Pattern Matching tool goes to work, all without any coding.

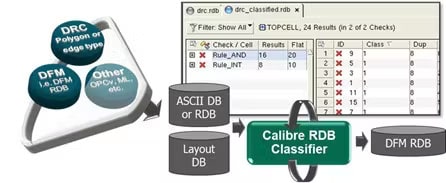

Layout verification errors can overwhelm a designer, so there’s a feature to organize and manage verification data through the Results DataBases (RDB) Classifier, using layout context and groups for similar results, so that repetitive errors like cell arrays are quickly identified.

Example

An unnamed customer had issues with an IC showing audio distortion, and by using Calibre Pattern Matching they were able to quickly find symmetry violations. Manual measurements and cell mirroring weren’t sufficient to find these violations. Early identification improved design quality and reduced layout rework. IP placements were verified early in the design, instead of late, saving time. Less time was required for physical verification, so a shift-left approach really worked.

Summary

Custom and analog mixed-signal designs are complex to layout and can take much engineering time to meet the specifications. By using a methodology of early IP placement verification and interactive symmetry checking, designers can more quickly find and fix issues, cutting down time to market.

Read the technical paper online, Shift Left with Calibre Pattern Matching: Trust in design practices but verify early and frequently.

Related Blogs

- Getting Faster DRC Results with a New Approach

- Design Stage Verification Gives a Boost for IP Designers

- A Game-Changer for IP Designers: Design Stage Verification

- Layout Pattern Matching for DRC, DFM, and Yield Improvement

Comments

There are no comments yet.

You must register or log in to view/post comments.