On big chip design projects the logic verification effort can be larger than the design effort, taking up to 70% of the project time based on data from the 2022 Wilson Research Group findings. Sadly, the first silicon success rate has gone downwards from 31 percent to just 24 percent in the past 8 years, causing another spin to correct the flaws, costing companies lost time to market and certainly hurting their revenue plans. Better verification would certainly improve first silicon success, but that is easier said than done.

Some other sobering numbers from the Wilson Research Group study:

- ASIC – 24% first time success, 36% finish on time

- FPGA – 16% achieve zero bug escapes, 30% finish on time

Design verification has many difficult chores: debugging, creating tests then running engines, testbench development and test planning. Ideally your team wants to minimize turn-around times, reach verification closure with the fewest people and compute resources, meet safety compliance, and know when the design quality is high enough to stop verifying, while meeting the project schedule.

I recently got an update from design verification expert Darron May at Siemens EDA to hear about something just announced, called Questa Verification IQ. Their approach is all about data-driven verification formed around using traceability, collaboration and analytics powered by AI/ML. Traditional analytics provided limited productivity and insight into just describing and diagnosing logic behavior, while big data-driven analytics using AI/ML offer predictive and prescriptive actions for verification. Software and hardware teams are becoming more productive by collaborating through the use of CI (Continuous Integration), Agile methods, ALM (Application Lifecycle Management), cloud-based design, and applying AI/ML techniques. Safety critical industries have a need for traceability between requirements, implementation and verification, as defined in industry standards like ISO 26262 and DO-254.

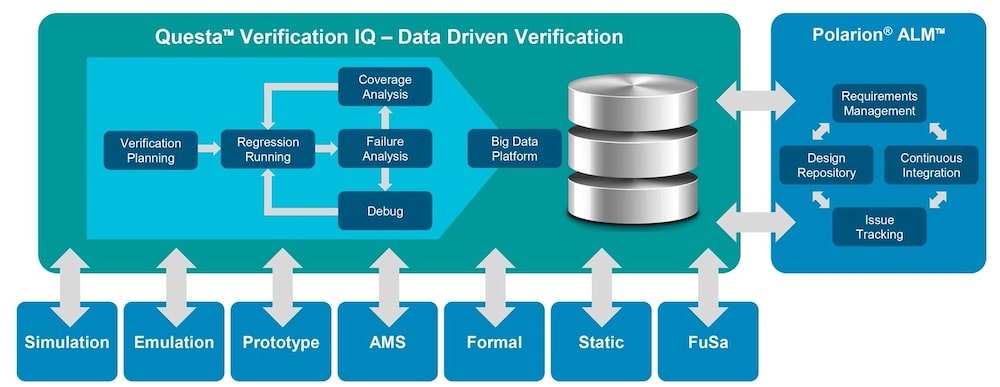

Here’s the big picture of how Quest Verification IQ connects together all of the data from various verification engines into a data-driven flow, along with an ALM tool.

The coverage data is gathered from logic simulation (Questa), Emulation and Prototyping (Veloce), AMS (Symphony), Formal (OneSpin), Static and FuSa. The ML feature analyzes all of this data in order to predict patterns and reveal any holes, point out root causes, then prescribe action to improve coverage. The ALM shown is Polarion from Siemens, although you could use another ALM, just like you can use your favorite verification engines.

Questa Verification IQ is a browser-based framework that includes a process guide so that you can build a safety critical flow using lifecycle management to plan and track all requirements. The regression navigator enables your team to create and execute tests, monitor the results, and have a complete verification history. With the coverage analyzer you know how complete your coverage is for code, functional blocks and test plans. Finally, the data analytics presented provide you with a metric platform, using project dashboards and providing cross analytics.

The web-based framework scales for any size of electronics project, and you won’t have to install any software or be concerned about keeping your OS updated. It also supports public, private or hybrid cloud setups. With AI/ML being applied the verification closure process is sped up, while debug effort quickens as root cause analysis helps pinpoint where to improve.

I asked Darron May a few clarifying questions.

Q: Can I mix and match Questa Verification IQ with any EDA vendor tool and ALM?

A: Questa Verification IQ supports ALM tools and engines via a standards based approach. It interfaces with ALM tools using Open Services for Lifecycle Collaboration (OSLC) so any tool supporting the standard like Doors next or Siemens Polarion and Teamcenter can be used. Any engine can be launched by Questa Verification IQ and again we have support for coverage via the Unified Coverage Interoperability Standard (UCIS).

Q: How does this approach compare to Synopsys DesignDash?

A: Synopsys DesignDash is focused on ML for design data whereas Questa Verification IQ is focused on data driven verification using analytics, including ML, to accelerate verification closure, reduce turn-around times and provide maximum process efficiency. Questa Verification IQ provides applications needed for team-based collaborative verification management in a browser-based framework with centralized access to data.

Q: How does this approach compare to Cadence Verisium?

A: Cadence Verisium focuses only on ML assisted Verification. In comparison Siemens Questa Verification IQ provides complete data driven verification solution powered by Analytics, Collaboration and Traceability. Verification Management is provided in a browser-based tool with applications built around Collaboration. Coverage Analyzer brings the industry’s first collaborative coverage closure tool using analytical navigation assisted by ML. Question Verification IQ interfaces with Siemens Polarion using OSLC and provides a tight digital thread traceability with Application Lifecycle Management with no UI context change, bringing the power of ALM to hardware verification.

Summary

I’m always impressed with new EDA tools that make a complex task easier by working smarter, not requiring engineers to put in more hours of manual effort. With early endorsements of Questa Verification IQ from familiar companies like Arm and Nordic Semiconductor, it looks like Siemens EDA has added something compelling for verification teams to consider looking at.

Related Blogs

- Coverage Analysis in Questa Visualizer

- EDA in the Cloud with Siemens EDA at #59DAC

- New Mixed-Signal Simulation Features from Siemens EDA at DAC

- Faster Time to RTL Simulation Using Incremental Build Flows

Comments

There are no comments yet.

You must register or log in to view/post comments.