In the 1970’s we designed ICs first and when silicon came back then we measured the power and junction temperature. At that time there were no EDA simulation tools or models for full-chip power and temperature analysis. Fast forward to 2013 and we find that temperature and power are still demanding requirements for MPSoC (multi-processor SoC) projects. Ideally you want to measure and control both power and temperature during the design phase of your project, instead of after manufacturing when it’s too late.

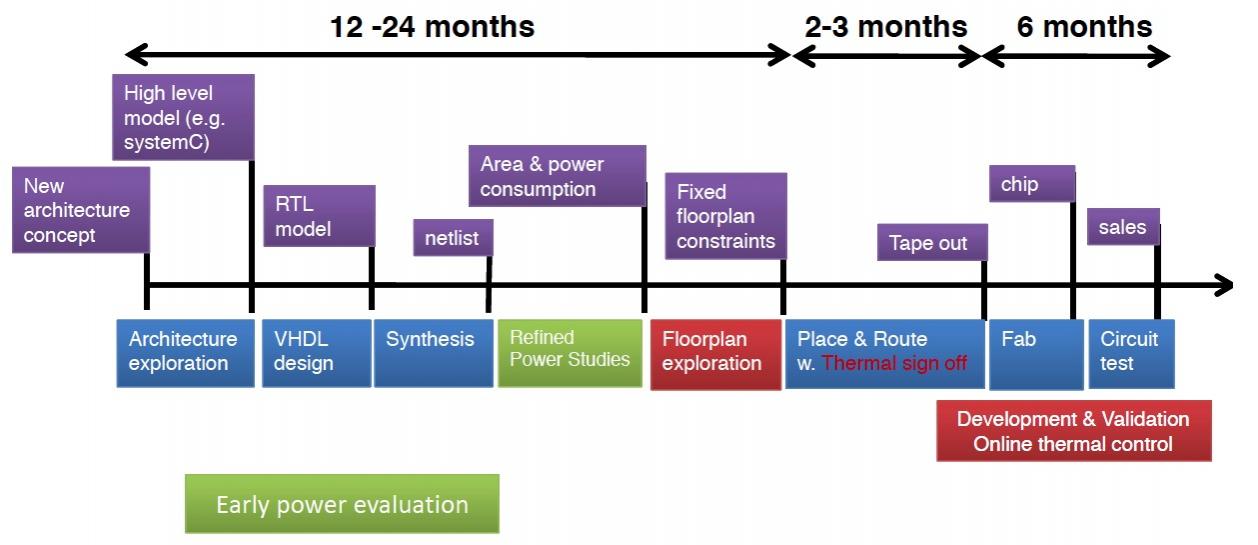

One approach for power and thermal analysis is to wait until you have an architecture explored, RTL models created and use logic synthesis to create a gate-level netlist:

The big drawback of such an approach is that you have not been able to look at early HW/SW interaction and how it impacts the thermal effects. There are some EDA tools available today for thermal analysis:

- Package/board and cooling design – FloTherm (Mentor Graphics)

- Post-layout level – Heatwave (Gradient DA)

- Thermal modeling – HotSpot (University of Virginia)

- Thermal emulator – 3D-ICE (EPFL)

The first two tools are rather low-level, so they are not viable for platform-level exploration. The last two tools are more high-level, and are not yet commercial, yet don’t link with a virtual prototype approach. There are virtual platforms today that may use power models, however there aren’t really any thermal models ready.

At DAC this year there was a presentation by Pascal Vivet from CEA-Leti, a research group in Grenoble, France. The presentation was titled: Early Validation of MPSoCs Thermal Mitigation through Integration of Thermal Simulation in SystemC Virtual Prototyping.

Pascal Vivet, CEA-Leti

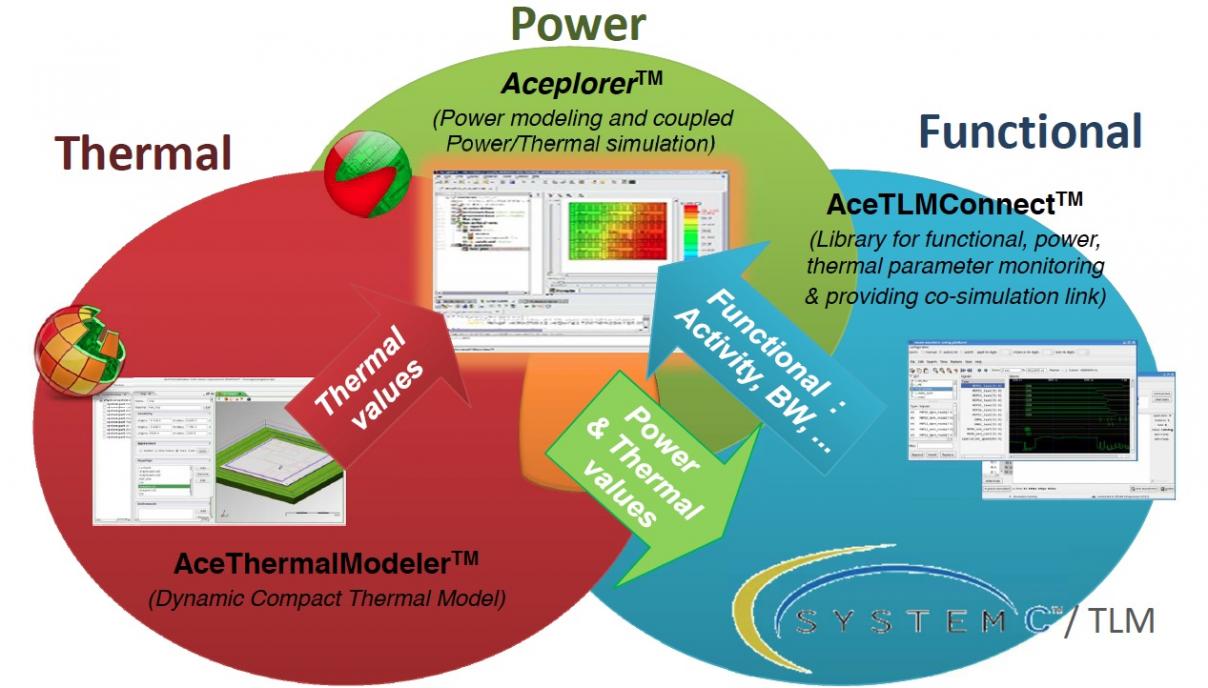

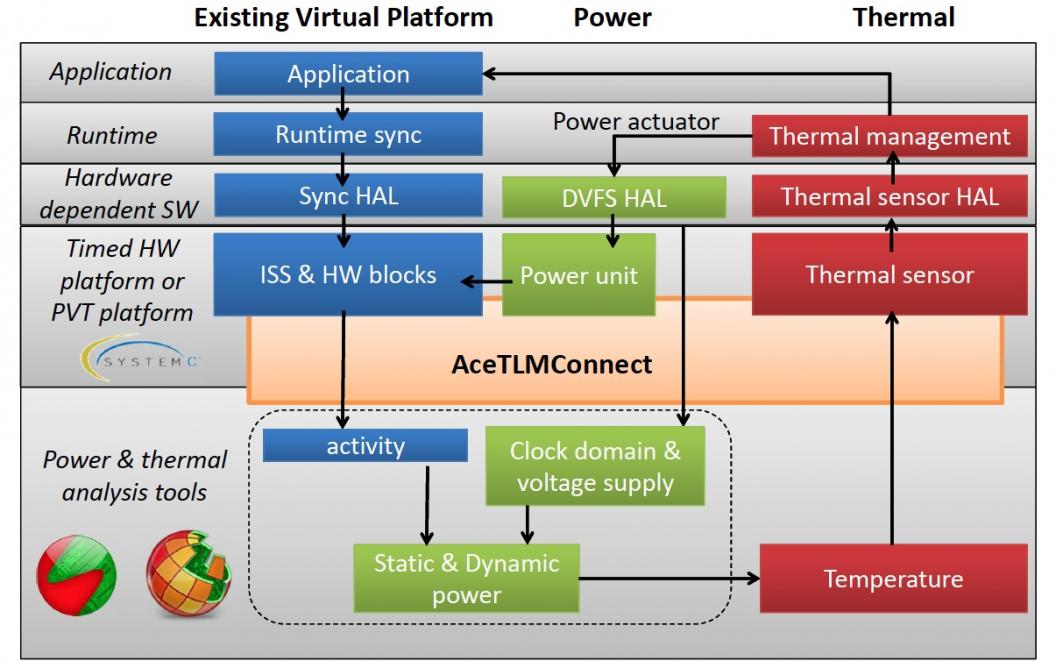

Pascal’s group used ESL tools from Docea Power to enable early thermal and power analysis while running SW.

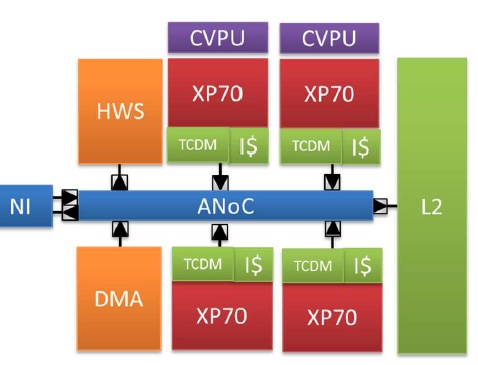

They designed a quad core chip called LOCOMOTIV using a processor called the XP70, and it’s connected to a shared memory with an asynchronous NoC. For power control there’s a block called the CFP unit that monitors the power, voltage and temperature of the system. This MPSoC uses an adaptive voltage and frequency scaling on each core to adapt to process, aging and temperature variations.

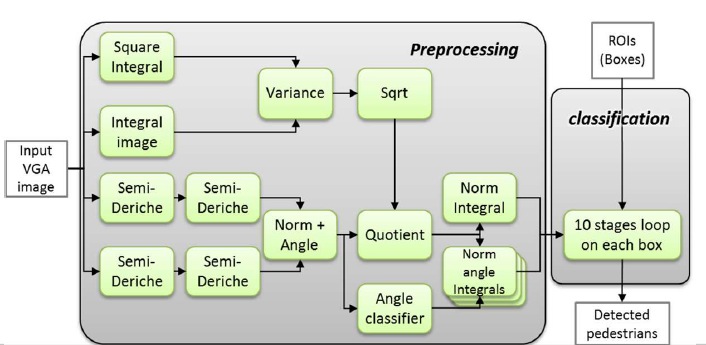

The application was for pedestrian detection where a camera system is connected to the MPSoC.

A power and thermal aware virtual platform approach was used to model how actual SW effects performance at the earliest possible stage.

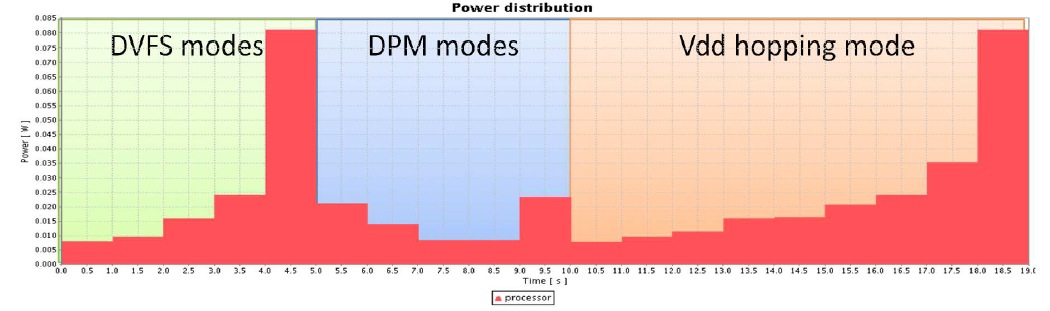

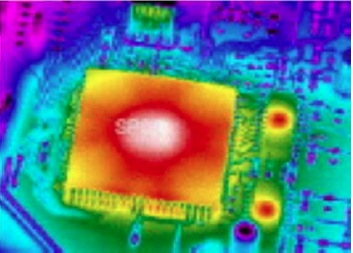

Results from power modeling are shown for three different operating modes:

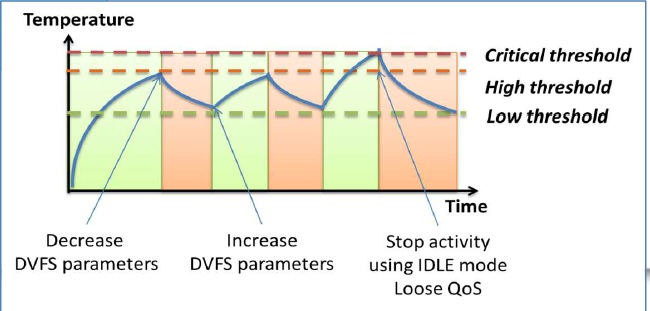

The approach to thermal management is to set temperature thresholds and apply DVFS decreases or increases.

With the use of idle time management, slack reclamation and thresholds the thermal budget of T < 95 degrees C was met, and the peak temperature was limited to 91.2 degrees C. At the ESL level the thermal simulation run time was only 16 minutes.

Summary

Engineers from CEA-Leti were able to design a MPSoC system and use a thermal, power and functional ESL design flow. EDA tools from Docea Power were used, and ST supplied the camera sub-system.

Benefits of a virtual platform approach included:

- Improve safety/reliability due to thermal issues

- Support thermal management development before hardware is available, providing a shorter time to market

- Co-simulation approach between HW and SW

Read the complete DAC presentation here: .

lang: en_US

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era