Layout editing is a complex task, traditionally done manually by designers, and the layout design productivity largely depends on the designer’s skills and expertise. However, a good tool with features for ease of design is a must. Layout productivity has been an area of focus and various features are constantly being added in layout editing tools for designers to quickly draw the layout. While that continues, we have yet another dimension of looking at the layout productivity. With the advent of SoCs, deep-submicron designs and varying integrated functionalities on a single chip, layout designing is no longer a job of a few designers. It needs a substantial team of designers to work on different parts of a layout and frequent synchronization between them. This again is a time consuming process and needs attention. It becomes extremely critical at the time of tape-out when chip finishing is done on the entire top level layout.

While reviewing Mentor Graphics Pyxis Layout Suite, I came across “Pyxis Concurrent”; what an excellent idea! I was amazed to see the on-line demo (link mentioned at the end). Mentor has rightly and pro-actively identified the need for multiple designers to edit different parts of the same cell and enabled them to do it concurrently, hence accelerating the layout development process and the tape-out time.

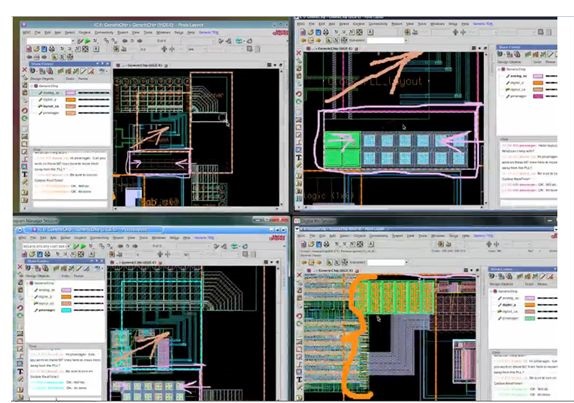

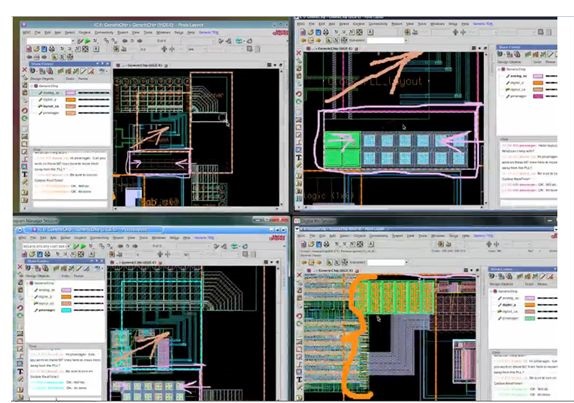

[Different parts of the layout being done simultaneously]

Designers can define their work area by creating fences and work on the same cell in shared mode over the network. The shared session is owned by the layout captain. Any edits to cell, path or shape is local to the designer who edits them until he/she saves the design. At the time of saving the design, a message is broadcasted to all designers. Data integrity is maintained as the changes by designers within their fences are local to them until a design save is done. All the typical editing commands such as edit, move, delete, undo stack etc. are supported locally to a designer for that portion of the layout. At the same time, any designer is free to view other portions of the design and provide message / feedback, on any part of the design as appropriate, to other designers.

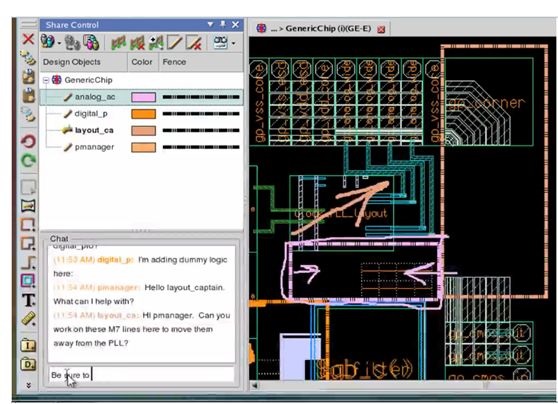

[A Designer pointing to a layout area and communicating through chat box]

The suite provides a virtual white board and chat service for effective team interaction. Any designer can exactly pin-point the other layout joints, shapes, components and so on which may need modification and use chat area to communicate with other designers.

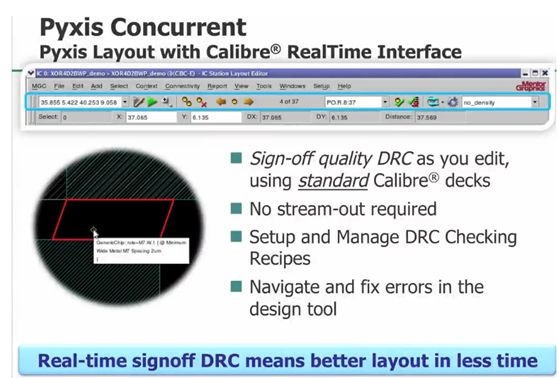

[Calibre real time interface with Pyxis]

Interestingly, this concurrent layout editing environment is seamlessly integrated with Realtime Calibre verification for on-line DRC checks which is especially important during chip finishing for DRC and other corrections and verification done by designers and the whole team certifying the chip layout together. A designer can just check his/her portion by running Calibre, hence keeping the layout DRC correct all the time.

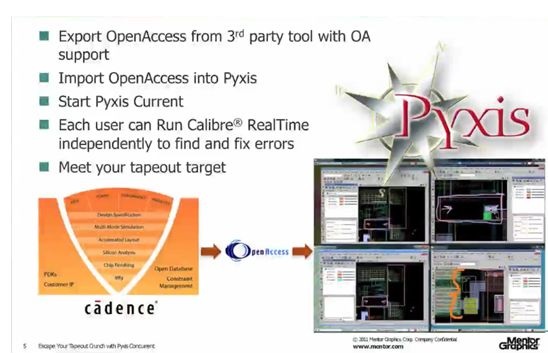

[Interoperability with third party layout]

Design data interchange is supported through both GDS and OpenAccess. Any third party layout can be imported into Pyxis layout suite and integrated into the design with ease.

For an exciting on-line demo, just click DEMO

The Pyxis Project Manager provides comprehensive integration with design kits, schematic development, design verification, floorplanning, custom routing etc. for the complete layout flow for block as well as complete chip.

Share this post via:

Comments

0 Replies to “Real Time Concurrent Layout Editing – It’s Possible”

You must register or log in to view/post comments.