Berkeley DA coined the phrase “Analog FastSPICE”, and I’ve been getting an update from them at DAC for several years now. In Austin I met with Paul Estradathe COO and Patrick Muyshondt.

Paul Estrada

Paul Estrada, COO (circa 2010)

Q: What’s new this year for BDA?

We announced Analog FastSPICE Mega earlier this year for 100M element capacity.

Q: Who is using this new circuit simulator?

TSMC = adopting MEGA for internal IP use on Memories.

Q: What is unique about Mega?

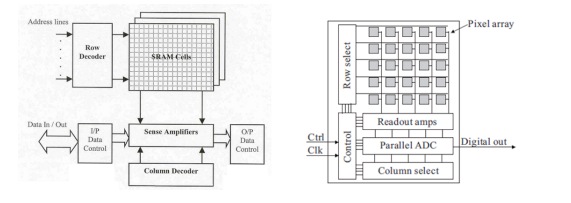

First silicon accurate, memory simulator or any array. Embedded SRAM (Most users), NVM, CMOS image sensors, DRAM.

Q: What other simulators do you offer?

AFS Nano – Lite version, only $1,900

Analog FastSPICE – Flagship circuit simulator

Q: What circuits are well-suited for mega?

AFS Mega – embedded SRAM and NVM, for accuracy and capacity.

Above AFS Mega – anything partitioned.

Q: How much RAM does Mega use?

128GB of RAM to reach 100M elements in AFS Mega.

Q: How do your FastSPICE simulators compare to the competition?

Competition – we are about 2X – 6x faster than FineSim SPICE

Our Accuracy – .01% to 1% inaccurate compared to SPICE

Speed – beating FastSPICE tools with 10X better accuracy, about some speeds to 5X faster.

Q: What are the inputs to Mega?

AFS Mega – accepts RLCM, s-parameters (all our simulators)

Q: What are the types of analysis for Mega?

AFS Mega Analysis – Transient, DC, Tran with temp, MC, alter, sweep (not freq & noise).

Models – same as AFS

Q: What trends do you see for circuit simulation now?

In the olld days for memory simulation: HSIM for big & Fast, HSPICE for accurate but smaller designs.

Last 5 years – FineSim Pro for big & fast, FineSim SPICE for accurate.

Now with AFS Mega – one simulator for both big&fast, accurate.

– not patented, proprietary techniques.

Q: How does Mega work, and how do you use it?

SPICE-accurate architecture, same code as AFS, no partitioning, no block-level tuning, no events, no tables, no coupling cap grounding, no cap approximation, no skipping of convergence steps

– no tuning, no modes, no config stups, no delay vs power tuning

Some global settings

Delay resolution: 1fs, 1pa current, accurate leakage current, accurate mc (not table look ups), accurate Verilog A.

Q: Does Mega co-simulate with HDL simulators?

AFS-AMS to handle Verilog AMS. Not yet enabled on AMS Mega.

Q: Is Mega certified by any foundries?

Yes, Mega is foundry certified on both HSPICE and Spectre formats for models.

Q: What type of parasitic netlists does Mega accept?

Parasitics – flat extracted and DSPF BA.

Q: How does licensing work?

Licensing: 10M mos elements & 8 threads. Add more licenses as needed.

Q: What should I expect to see in the next year?

In next 12 months: Add more capabilities in AFS Mega like AFS (like AMS), more performance and capacity.

Patrick Muyshondt

Q: What’s new at DAC?

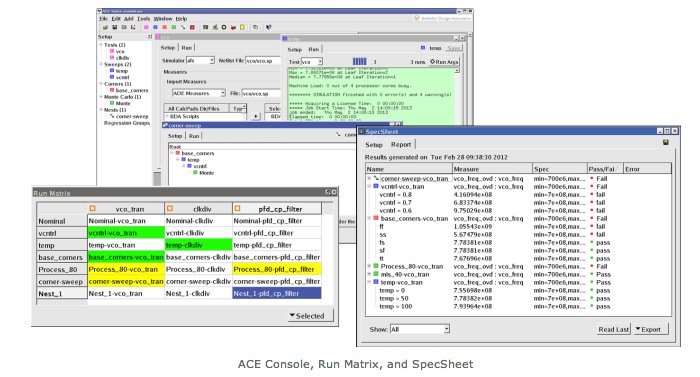

Something we call ACE – Analog Characterization Environment

– YOu have an AMS block, will it work against all variations?

Q: How does it work?

Command line or from ADE in Cadence. Works with AFS, HSPICE or Spectre (coming soon).

Q: How do I control it?

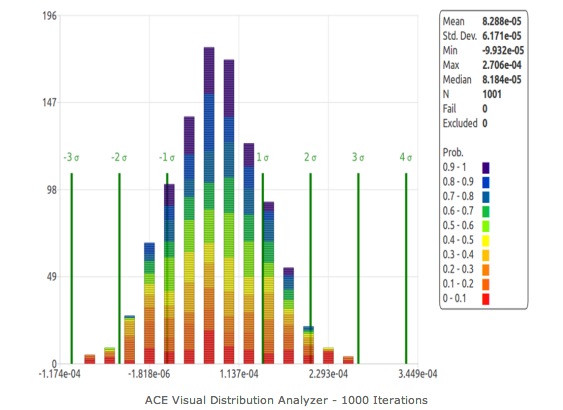

Combinations of: PVT, Sweeps, MC.

Q: What is the output?

End result: Spec sheet, all char runs, did I pass or fail. Visualize the results and analyze the results.

Did my Tests pass or fail? Test: netlist, stim, analysis, measures.

Input demo: PLL. Import measures. (Freq, current, power: Min, Max). Stored in an XML file for easy integration.

Customers: Just announced, stay tuned to hear.

1) Setup and define tests

2) Use Multi-core and Multi-threading. Automatically schedule to each core, 1 license per four cores, may use an LSF queue.

Idea: internally conceived and developed.

Replacing ad-hoc characterization with easy characterization.

Easy to sweep temperature. Designer defines what needs to be varied, not doing auto-input stimulus.

Much easier to use than ADE XL, but we didn’t really look at it. Learning curve is minutes.

Tests – exported/imported or re-used.

Tests/Sweeps, corners, MC.

What about a Processor corner and do a sweep across voltage (cannot be attempted in ADE), we do it in 10 seconds or so. Drag and drop setup using a GUI.

Nests – GUI-created tests.

Before I submit a new test I can see how many SPICE runs will be launched.

*lang: en_US

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center