It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your own sentences here about mobile, battery-life, datacenters, cloud computing and why this is making power so important. Or you can talk about “dark silicon”, putting a lot of functionality on a chip but then not being able to light it all up. Or how about FinFETs and reducing leakage power. Whatever your design is doing, keeping its power low is almost certainly one of the things you are having to worry about.

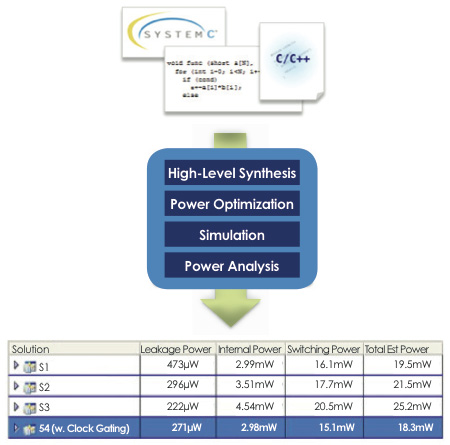

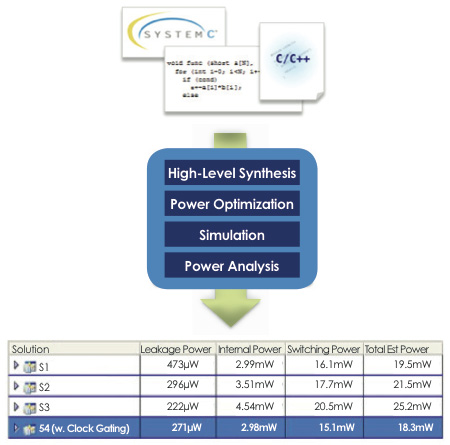

What goes for design in general also goes for high-level synthesis (HLS). Historically, HLS has traded off performance and area. Want higher performance? Instead of re-using that multiplier put a second one on the chip. But that is no longer good enough since performance doesn’t just come at the cost of area, it also comes at the cost of power. As is almost always the case, optimization at higher levels of abstraction can make larger gains than trying to recover later in the design cycle. So optimization for power at the C++/SystemC level offers more opportunity than at RTL which offers more than at the gate level.

Calypto’s Catapult LP was created to address this, enabling area and power optimization when synthesizing designs from C++ and SystemC. Catapult LP automatically inserts power saving techniques during high level synthesis, driven by the constraints the user provides.

So what sort of power saving techniques can be used?

- Numerical refinement: by allowing all calculations to be optimized for the exact bit-widths necessary, the sizes of registers and buses can be reduced saving power (dynamic and static).

- Interfaces: if a design is making repeated use of memory and buses, the interface can be made wider to do multiple reads and writes at once and store the data locally.

- Pipeline architecture: many algorithms are highly dependent on pipeline architectures and the associated memory/register toggle rates

- Clock frequency: by reducing the clock frequency and forcing HLS to find architectures that can live with the lower clock rate can result in significant power saving

- Multiple clocks: blocks with lower data rates can be run at lower clock rates. Catapult supports multiple clocks.

- Latency and throughput: different tradeoffs between latency and throughput can also reduce power significantly.

- Idle: Catapult can insert an idle signal into a block, set when the block is not doing any processing. This can be used as part of the system level power management to suppress or slow clocks.

- Sequential clock gating: by analyzing flows of data it is often possible to suppress clocking all registers when it is clear that the value is not changing.

Download the Calypto white-paper Catapult LP for a Power Optimized ESL Hardware Realization Flow on their website here. There is also a webinar How to Optimize for Power with High Level Synthesis on March 12th at 10am Pacific. Registration is here.

Or see Calypto at booth 705 at DVcon this week (Tuesday/Wednesday, 3.30 to 6.30).

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center