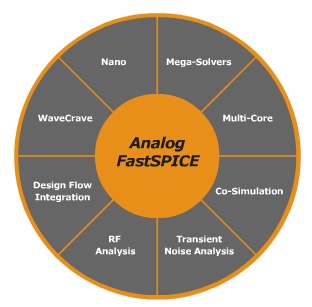

Paul Estrada, COO of Berkeley DA met with me on the final day of DAC to provide an update. BDA coined the phrase Analog FastSPICE and have continued to dominate that market segment in the world of SPICE circuit simulators.

Notes

What’s New – More customers this year, better accuracy (10 to 15 db lower noise floor), by default multi-threaded on 4 cores (about 2.5X faster than 1 core), 10 million elements. Sample P noise – periodic noise analysis (ADC, any periodic circuit, image sensors).

Next year – Faster, higher capacity.

VCS supported for co-simulation (Incisive, ModelSim, VCS, Aldec Riviera Pro)

Tanner EDA – same executable but Tanner specific license to limit the features (standard SPICE plus transient noise).

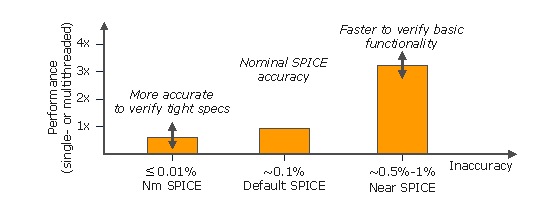

WHy choose BDA? Accuracy, capacity, performance. Big circuits, actually measure device noise analysis (ADC, DAC, PLL, high-speed IO, DLL, RF IC, CMOS image sensors).

Magma acquisition – designers have used FineSim and HSIM, but now they want an independent simulator for Memory circuits which creates an opportunity for BDA. Synopsys has too many circuit simulators, so what is the product road map?

Also see:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?