As an IC designer I absolutely loved embarking on a new design project, starting with a fresh, blank slate, not having to use any legacy blocks. In the early 1980’s we really hadn’t given much thought to re-using semiconductor IP because each new project typically came with a new process node, so there was no IP even ready… Read More

Crossfire Baseline Checks for Clean IP at TSMC OIP

IP must be properly qualified before attempting to use them in any IC design flow. One cannot wait to catch issues further down the chip design cycle. Waiting for issues to appear during design verification poses extremely high risks, including schedule slippage. For example, connection errors in transistor bulk terminals where… Read More

Affordable EDA Tools for IoT Designs, Guess which Vendor

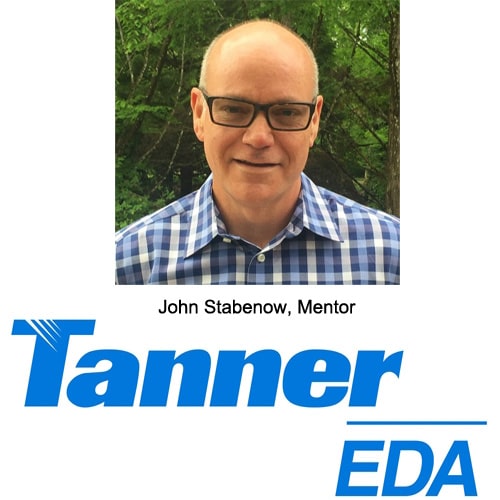

I just had to drive my car 7 miles from Tualatin, Oregon to visit with an EDA veteran who has played a lot of diverse roles in his career, including: IC Mask Designer, Layout Manager, Account Manager, Business Development, Director, Foundry Relations Director. His name is John Stabenow, with Mentor, a Siemens Business, and we met… Read More

Improving Yield and Reliability with In-Chip Monitoring, there’s an IP for that

There’s an old maxim that you can only improve what you measure, so quality experts have been talking about this concept for decades and our semiconductor industry has been the recipient of such practices to such an extent that we can now buy consumer products that include chips with over 5 billion transistors in them. You’ve… Read More

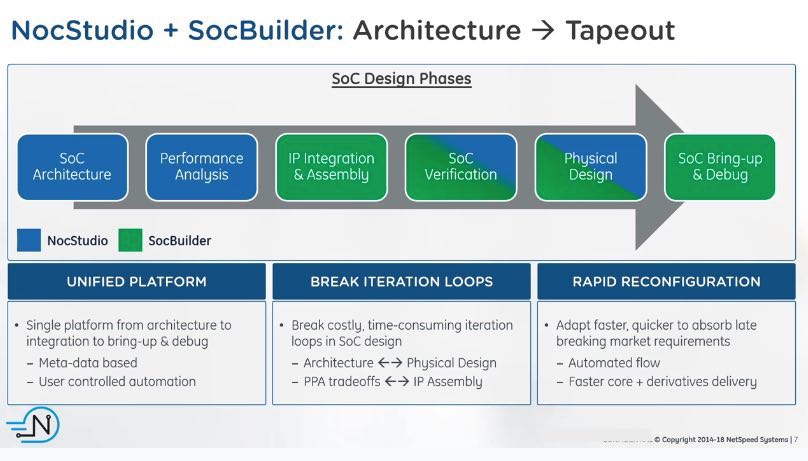

Webinar: NetSpeed is about to change the way SOCs are designed

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

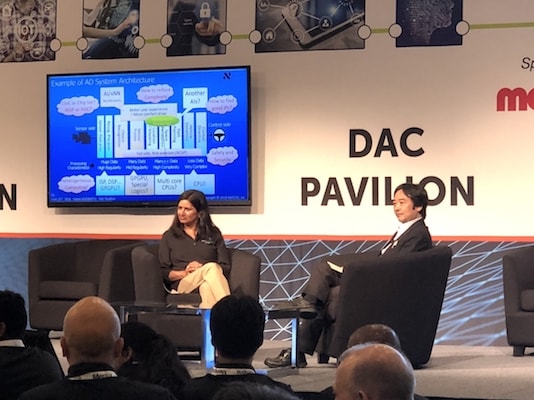

Netspeed and NSITEXE talk about automotive design trends at 55DAC

DAC is where both sides of the design equation come together for discussion and learning. This is what makes attending DAC discussion panels so interesting; you are going to hear from providers of tools, methodologies and IP as well as those who need to use them to deliver working solutions. There are few places where the interplay… Read More

Optimization and Reliability for FinFET designs at #55DAC

TSMC is the leading foundry worldwide and they make a big splash each year at the DAC exhibit and conference, so I stopped by their theatre area during the presentation from IP vendor Moortec to see what’s new this year. Stephen Crosher was the presenter from Moortec and we had exchanged emails before, so this was the first time… Read More

Maximize Bandwidth in your Massively Parallel AI SoCs?

Artificial Intelligence is one of the most talked about topics on the conference circuit this year and I don’t expect that to change anytime soon. AI is also one of the trending topics on SemiWiki with organic search bringing us a wealth of new viewers. You may also have noticed that AI is a hot topic for webinars like the one I am writing… Read More

Drop-In Security for IoT Edge Devices

You’re excited about the business potential for your cool new baby monitor, geo-fenced kid’s watch, home security system or whatever breakthrough app you want to build. You want to focus on the capabilities of the system, connecting it to the cloud and your marketing rollout plan. Then someone asks whether your system is architected… Read More

55DAC Trip Report IP Quality

This year I signed books in the Fractal booth (compliments of Fractal) and let me tell you it was quite an experience. IP quality is a very touchy subject and the source of many more tape-out delays than I had imagined. As it turns out, commercial IP is the biggest offender which makes no sense to me whatsoever. Even more shocking, one… Read More