You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14433

[name] => X-Subscriber

[slug] => x-subscriber

[term_group] => 0

[term_taxonomy_id] => 14433

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 0

[filter] => raw

[cat_ID] => 14433

[category_count] => 0

[category_description] =>

[cat_name] => X-Subscriber

[category_nicename] => x-subscriber

[category_parent] => 0

[is_post] =>

)

Imagination seems to be well known for a couple of things. Firstly, everyone knows that it is the graphics processor used in the iPhone and the iPad and lots of other phones. And they know that Imagination acquired MIPS at the start of this year.

But what people don’t seem to really appreciate is just what a huge portfolio of IP… Read More

I remember during my first ten years as a software developer, I used many different computers such as IBM mainframes, Apollo and Sun workstations, and VAX computers. During that time I also bought my first home computer, a Macintosh. I didn’t of course think of this at the time, but the one thing they all had in common was that they did… Read More

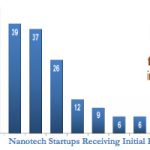

At the recent GSA Entrepreneurship Forumone of the panelists was Angel Orrantia of Innopartners who are trying a novel approach to funding startups in the semiconductor space and the surrounding ecosystem.

It seems things got started with an innovation center inside SK Hynix. Just in case you have forgotten, Hynix is the newish… Read More

How do you benchmark a processor? It seems like it should be easy, just run some code and see how fast it is. Traditionally processors were indeed benchmarked by raw performance like GMACS, GFLOPS, memory bandwidth and so on. But in today’s world where systems have become very complex and applications very compute intensive, the… Read More

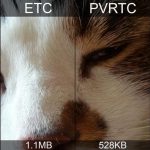

The 80s called, and they want lazy programming back. Remember “Mr. Mom”? Michael Keaton is talking about rewiring the house, and Martin Mull asks if he’s going to use all 220V, and Keaton responds “Yeah, 220, 221, whatever it takes.” Not knowing what’s inside can make you look silly.

Such is the case with OpenGL ES. Taking a look at … Read More

There are several events in Silicon Valley coming up of general interest to people working in EDA and the semiconductor industry.

SEMI 16th Annual Valley Lunch Forum. August 22nd, 11.30am to 1.30pm, Santa Clara Marriott

- What are the Opportunities for Advanced Semiconductor Devices?

- Where will the year end for 2013?

- Will we have

…

Read More

Your cell-phone contains a camera. In fact, it probably contains two: one forward facing for video-calls and one rear-facing for taking photographs and videos. The rear-facing one typically has much higher pixel count than the front-facing. The capabilities of cell-phone cameras are getting “good enough” that… Read More

You have probably heard of the Internet of Things or IoT. This is the future world in which not only are our computers and smartphones connected to the internet, but all sort of other things like thermostats, medical monitors, smart car-keys and soil analyzers. What these “things” have in common is that, unlike computers… Read More

Everyone understands that as we increasingly focus on the design of mobile devices, there is an increasing focus on low power. But, what is implied in designing for low-power? Designing for low power means we have to work with multiple power domains and multiple clock domains—making our design task more complex. We also must get… Read More

IP: Make or Buy?by Paul McLellan on 07-30-2013 at 2:02 pmCategories: Arasan, IP

A couple of weekends ago I moderated a panel session for the Chinese American Semiconductor Professional Association. No, I had no idea such an organization existed either (at least partially because I’m not Chinese). Dan Nenni was meant to be doing it but he went off to Las Vegas, so I ended up getting the job. On a Saturday … Read More