2.5D and 3D multi-die design is rapidly moving into the mainstream for many applications. HPC, GPU, mobile, and AI/ML are application areas that have seen real benefits. The concept of “mix/match” for chips and chiplets to form a complex system sounds deceptively simple. In fact, the implementation and analysis techniques required… Read More

The Immensity of Software Development and the Challenges of Debugging Series (Part 4 of 4)

The Impact of AI on Software and Hardware Development

Part 4 of this series analyzes how AI algorithmic processing is transforming software structures and significantly modifying processing hardware. It explores the marginalization of the traditional CPU architecture and demonstrates how software is increasingly dominating… Read More

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early Adopters

The demand for high-performance computing (HPC), data centers, and AI-driven applications has fueled the rise of 2.5D and 3D multi-die designs, offering superior performance, power efficiency, and packaging density. However, these benefits come with myriads of challenges, such as multi-physics, which need to be addressed.… Read More

The Immensity of Software Development and the Challenges of Debugging (Part 3 of 4)

Part 3 of this 4-part series analyzes methods and tools involved in debugging software at different layers of the software stack.

Software debugging involves identifying and resolving issues ranging from functional misbehaviors to crashes. The essential requirement for validating software programs is the ability to monitor… Read More

Synopsys and TSMC Pave the Path for Trillion-Transistor AI and Multi-Die Chip Design

Synopsys made significant announcements during the recent TSMC OIP Ecosystem Forum, showcasing a range of cutting-edge solutions designed to address the growing complexities in semiconductor design. With a strong emphasis on enabling next-generation chip architectures, Synopsys introduced both new technologies and … Read More

The Immensity of Software Development and the Challenges of Debugging Series (Part 2 of 4)

Part 2 of this 4-part series reviews the role of virtual prototypes as stand-alone tools and their use in hybrid emulation for early software validation, a practice known as the “shift-left” methodology. It assesses the differences among these approaches, focusing on their pros and cons.

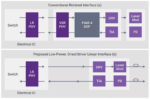

Synopsys Powers World’s Fastest UCIe-Based Multi-Die Designs with New IP Operating at 40 Gbps

As the demand for higher performance computing solutions grows, so does the need for faster, more efficient data communication between components in complex multi-die system-on-chip (SoC) designs. In response to these needs, Synopsys has introduced the world’s fastest UCIe-based IP solution, capable of operating at a groundbreaking… Read More

Linear pluggable optics target data center energy savings

Data center density continues growing, driving interconnect technology to meet new challenges. Two of the largest are signal integrity and power consumption. Optical interconnects can solve many signal integrity issues posed by copper cabling and offer support for higher frequencies and bandwidths. Still, through sheer… Read More

Synopsys IP Processor Summit 2024

Now that live events are filling up there are even more live events especially here in Silicon Valley. Synopsys, the #1 full IP provider, will host a processor summit here in Santa Clara next month. Given the popularity of anything RISC-V, I would expect this event to be very well attended so be sure and register in advance.

The networking… Read More

First third-party ISO/SAE 21434-certified IP product for automotive cybersecurity

Increased processing and connectivity in automobiles are cranking up the priority for advanced cybersecurity steps to keep roads safe. Electronic vehicle interfaces, including 5G/6G, Bluetooth, Wi-Fi, GPS, USB, CAN, and others, offer convenience features for drivers and passengers, but open numerous attack vectors for… Read More