Synopsys has been quite active lately in their messaging around formal verification. One such event at DVCon this year was a tutorial on some of the more advanced techniques/ methodologies that are accessible to formal teams, mostly presented by customers, though opened by a Synopsys presentation. The tutorial covered so many… Read More

Aart de Geus At the Heart of Impact!

At the Silicon Valley SNUG 2018, Synopsys Chairman and co-CEO Dr. Aart de Geuss gave his keynote speech addressing attendees on how far we have evolved, and at times encountered the aha factor that helps propel us to the next level. He explored trends as well as the current state of his company solution offerings.

Moore’s Law, Digital… Read More

Qualcomm, AMD on Verification with Synopsys

Synopsys hosts a regular lunch at DVCon each year (at least over the last few years I have checked), a nice meal and a show, opening a marketing update followed by 2-3 customer presentations on how they use Synopsys verification in their flows. This year’s event was moderated by Piyush Sancheti from Synopsys Verification marketing… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 2 of 2)

The second panel is about system coverage and big data. Coverage metrics have been used to gauge the quality of verification efforts during development. At system level, there are still no standardized metrics to measure full coverage. The emergence of PSS, better formal verification, enhanced emulation and prototyping techniques… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 1 of 2)

In the EDA space, nothing seems to be more fragmented in-term of solutions than in the Design Verification (DV) ecosystem. This was my apparent impression from attending the four panel sessions plus numerous paper presentations given during DVCon 2018 held in San Jose. Both key management and technical leads from DV users community… Read More

EDA and Semiconductor — Is There Growth In The Ecosystem?

The semiconductor industry has gone through several major transitions driven by different dynamics such as shift in business models (fab-centric to fab-less), product segmentation (system design house, IP developers) and end market applications (PC to cloud; and recently, to both automotive and Internet of Things — IOT’s,… Read More

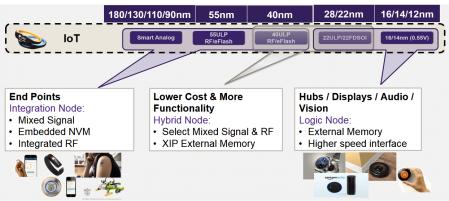

Analog-to-Digital Converter IP for IoT Designs

The projected revenue growth rate for IoT electronics remains strong, across a wide range of applications – e.g., visual object identification, voice recognition, machine automation, health and fitness applications, environmental and energy controls. A key component of these designs is the analog-to-digital conversion… Read More

Securing embedded SIMs

If you have a phone, you probably know it has a SIM card, for most of us the anchor that ties us into a 2/3-year plan with one network provider, unless you have an unlocked phone. Even then, you have to mess around swapping SIM cards if you travel overseas. Wouldn’t it be nice if the SIM was embedded and could be switched though an app or an… Read More

Webinar: Bottlenecks be Gone – Automated Performance Verification with Synopsys

Performance verification is among the most challenging of objectives in any SoC verification plan. It’s difficult to start effectively until quite late in the development cycle, at which point you don’t have a lot of time left to develop extensive performance-oriented testbenches. So many teams adapt functional tests to this… Read More

Data Security – Why It Might Matter to Design and EDA

According to the Economist, “The world’s most valuable resource is no longer oil, but data”. Is this the case?Data is the by-product ofmany aspects of recent technology dynamics and is becoming the currency of today’s digital economy. All categories in Gartner’s Top10 Strategic Technology Trends for 2018 (Figure… Read More