When talking about today’s sophisticated advanced node designs it’s easy to first think about the digital challenges. Yet, the effort to design the needed analog and mixed signal blocks for them should not be underestimated. The need for high speed clocks, high frequency RF circuits and high bit rate IOs makes the analog portions,… Read More

Synopsys Tutorial on Dependable System Design

Synopsys hosted a tutorial on the last day of DVCon USA 2022 on design/system dependability. Which here they interpret as security, functional safety, and reliability analysis. The tutorial included talks from DARPA, AMD, Arm Research and Synopsys. DARPA and AMD talked about general directions and needs, Arm talked about their… Read More

Synopsys Announces FlexEDA for the Cloud!

There’s been a lot of discussion and hype regarding use of the cloud for chip design for quite a while, more than ten years I would say. I spoke with Synopsys to better understand their recent Synopsys Cloud announcement to determine if it is different. Briefly, it is different, and here is why:

If you’re trying to design a complex SoC,… Read More

Use Existing High Speed Interfaces for Silicon Test

The growth of complexity for silicon test as it relates to test data volume and test times is driven by multiple concurrent factors. One dimension is simply the increase in silicon complexity. However, other factors are playing a role as well. These include higher reliability requirements for new applications such as automotive,… Read More

Getting to Faster Closure through AI/ML, DVCon Keynote

Manish Pandey, VP R&D and Fellow at Synopsys, gave the keynote this year. His thesis is that given the relentless growth of system complexity, now amplified by multi-chiplet systems, we must move the verification efficiency needle significantly. In this world we need more than incremental advances in performance. We need… Read More

Non Volatile Memory IP is Invaluable for PMICs

Power Management ICs are a vitally important part of system design. Evidence of this is cited by a Synopsys white paper that mentions how Apple acquired a portion of PMIC developer Dialog Semiconductor that was previously their exclusive PMIC supplier. Clearly Apple had decided that PMIC design was a strategic differentiating… Read More

Why It’s Critical to Design in Security Early to Protect Automotive Systems from Hackers

Remember when a pair of ethical hackers remotely took over a Jeep Cherokee as it was being driven on a highway near downtown St. Louis back in 2015? The back story is, those “hackers,” security researchers Charlie Miller and Chris Valasek, approached vehicle manufacturers several years before their high-profile feat, warning… Read More

Upcoming Webinar: 3DIC Design from Concept to Silicon

Multi-die design is not a new concept. It has been around for a long time and has evolved from 2D level integration on to 2.5D and then to full 3D level implementations. Multiple driving forces have led to this progression. Whether the forces are driven by market needs, product needs, manufacturing technology availability or EDA… Read More

Identity and Data Encryption for PCIe and CXL Security

Privacy and security have always been a concern when it comes to computing. In prior decades for most people this meant protecting passwords and locking your computer. However, today more and more users are storing sensitive data in the cloud, where it needs to be protected at rest and while in motion. In a Synopsys webinar Dana Neustadter,… Read More

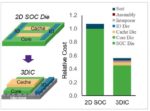

Heterogeneous Integration – A Cost Analysis

Heterogeneous integration (HI) is a general term used to represent the diverse possibilities for die technology incorporated into advanced 2.5D/3D packaging. At the recent International Electron Devices Meeting (IEDM) in San Francisco, a team from Synopsys and IC Knowledge presented data from analyses of future potential… Read More