These days, the term chiplets is referenced everywhere you look, in anything you read and in whatever you hear. Rightly so because the chiplets or die integration wave is taking off. Generally speaking, the tipping point that kicked off the move happened around the 16nm process technology when large monolithic SoCs started facing… Read More

PCIe 6.0: Challenges of Achieving 64GT/s with PAM4 in Lossy, HVM Channels

As the premier high-speed communications and system design conference, DesignCon 2023 offered deep insights from various experts on a number of technical topics. In the area of high-speed communications, PCIe has a played a crucial role over the years in supporting increasingly higher communications speed with every new revision.… Read More

Optimization Tradeoffs in Power and Latency for PCIe/CXL in Datacenters

PCI Express Power Bottleneck

Madhumita Sanyal, Sr. Technical Product Manager, and Gary Ruggles, Sr. Product Manager, discussed the tradeoffs between power and latency in PCIe/CXL data centers during a live SemiWiki webinar on January 26, 2023. The demands on PCIe continue to grow with the integration of multiple components… Read More

Synopsys Design Space Optimization Hits a Milestone

I talked recently with Stelios Diamantidis (Distinguished Architect, Head of Strategy, Autonomous Design Solutions) about Synopsys’ announcement on the 100th customer tapeout using their DSO.ai solution. My concern on AI-related articles is in avoiding the hype that surrounds AI in general, and conversely the skepticism… Read More

Podcast EP141: The Role of Synopsys High-Speed SerDes for Future Ethernet Applications

Dan is joined by Priyank Shukla, Staff Product Manager for the Synopsys High Speed SerDes IP portfolio. He has broad experience in analog, mixed-signal design with strong focus on high performance compute, mobile and automotive SoCs and he has a US patent on low power RTC design.

Dan explores the use of high-speed SerDes with Priyank.… Read More

Webinar: Achieving Consistent RTL Power Accuracy

A comprehensive report from the US Department of Energy (DOE), “Semiconductor Supply Chain Deep Dive Assessment” (February 2022) calls for a 1000X energy efficiency improvement that is required to maintain future compute requirement needs given a finite amount of world energy production. Energy efficiency is at the top of … Read More

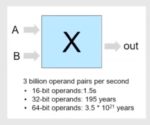

Formal Datapath Verification for ML Accelerators

Formal methods for digital verification have advanced enormously over the last couple of decades, mostly in support of verification in control and data transport logic. The popular view had been that datapath logic was not amenable to such techniques. Control/transport proofs depend on property verification; if a proof is … Read More

How to Efficiently and Effectively Secure SoC Interfaces for Data Protection

Before the advent of the digitized society and computer chips, things that needed protection were mostly hard assets such as jewelry, coins, real estate, etc. Administering security was simple and depended on strong guards who provided security through physical means. Then came the safety box services offered by financial … Read More

Synopsys Crosses $5 Billion Milestone!

“We intend to grow revenue 14% to 15%, continue to drive notable ops margin expansion and aim for approximately 16% non-GAAP earnings per share growth.”

Synopsys, Inc. (NASDAQ:SNPS) Q4 2022 Earnings Call Transcript

Synopsys is the EDA bellwether since they report early and are the #1 EDA and #1 IP company. In addition to crossing… Read More

Configurable Processors. The Why and How

Configurable processors are hot now, in no small part thanks to RISC-V. Which is an ISA rather than a processor, but let’s not quibble. Arm followed with configurability in Cortex-X. Both were considerably preceded (a couple of decades) by Synopsys ARC® RISC CPUs and CEVA DSPs. Each stressed configurability as a differentiator… Read More