At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. One of those panelists was the very personable Dr. Henry Sheng, Group Director of R&D in the EDA Group at Synopsys. Henry currently leads engineering for 3DIC, advanced technology and visualization.

Synopsys Accelerates First-Pass Silicon Success for Banias Labs’ Networking SoC

Banias Labs is a semiconductor company that develops infrastructure solutions for next-generation communications. Its target market is the high-performance computing infrastructure market including hyperscale data center, networking, AI, optical module, and Ethernet switch SoCs for emerging high-performance computing… Read More

Multi-Die Systems: The Biggest Disruption in Computing for Years

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. The discussion was based on a report published by the MIT Technology Review Insights in cooperation with Synopsys. This is a very comprehensive report (12 pages) that is available online HERE.

Here is the preface… Read More

Taking the Risk out of Developing Your Own RISC-V Processor with Fast, Architecture-Driven, PPA Optimization

Are you developing or thinking about developing your own RISC-V processor? You’re not alone. The use of the RISC-V ISA to develop processors for SoCs is a growing trend. RISC-V offers a lot of flexibility with the ability to customize or create ISA and microarchitectural extensions to differentiate your design no matter your application… Read More

Feeding the Growing Hunger for Bandwidth with High-Speed Ethernet

The increasing demands for massive amounts of data are driving high-performance computing (HPC) to advance the pace in the High-speed Ethernet world. This in turn, is increasing the levels of complexity when designing networking SoCs like switches, retimers, and pluggable modules. This growth is accelerating the need for … Read More

Takeaways from SNUG 2023

Synopsys pulled out all the stops for this event. I attended the first full day, tightly scripted from Aart’s keynote kick off to 1×1 interviews with Synopsys executives to a fireside chat between Sassine Ghazi (President and COO) and Rob Aitken (ex-Fellow at Arm, now Distinguished Architect at Synopsys). That’s a lot of … Read More

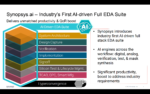

Full-Stack, AI-driven EDA Suite for Chipmakers

Semiconductor technology is among the most complex of technologies and the semiconductor industry is among the most demanding of industries. Yet the ecosystem has delivered incredible advances over the last six decades from which the world has benefitted tremendously. Yes, of course, the markets want that break-neck speed… Read More

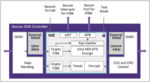

Securing Memory Interfaces

News of hackers breaking into systems is becoming common place these days. While many of the breaches reported to date may have been due to security flaws in software, vulnerabilities exist in hardware too. As a result, the topic of security is getting increased attention within the semiconductor industry around system-on-chip… Read More

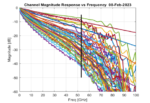

Power Delivery Network Analysis in DRAM Design

My IC design career started out with DRAM design back in 1978, so I’ve kept an eye on the developments in this area of memory design to note the design challenges, process updates and innovations along the way. Synopsys hosted a memory technology symposium in November 2022, and I had a chance to watch a presentation from SK hynix… Read More

Intel Keynote on Formal a Mind-Stretcher

Synopsys has posted on the SolvNet site a fascinating talk given by Dr. Theo Drane of Intel Graphics. The topic is datapath equivalency checking. Might sound like just another Synopsys VC Formal DPV endorsement but you should watch it anyway. This is a mind-expanding discussion on the uses of and considerations in formal which … Read More