The big fake news last week came from a report out of China stating that TSMC won a big Intel order for 3nm wafers. We have been talking about this for some time on SemiWiki so this is nothing new. Unfortunately, the article mentioned wafer and delivery date estimates that are unconfirmed and from what I know, completely out of line. … Read More

TSMC Explains the Fourth Era of Semiconductor – It’s All About Collaboration

The 32nd VLSI Design/CAD Symposium just occurred in a virtual setting. The theme of the event this year was “ICs Powering Smart Life Innovation”. There were many excellent presentations across analog & RF, EDA & testing, digital & system, and emerging technology. There were also some excellent keynotes, and this… Read More

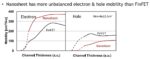

TSMC Design Considerations for Gate-All-Around (GAA) Technology

The annual VLSI Symposium provides unique insights into R&D innovations in both circuits and technology. Indeed, the papers presented are divided into two main tracks – Circuits and Technology. In addition, the symposium offers workshops, forums, and short courses, providing a breadth of additional information.

At… Read More

Highlights of the TSMC Technology Symposium 2021 – Automotive

At the recent TSMC Technology Symposium, TSMC provided a detailed discussion of their development roadmaps. Previous articles have reviewed the highlights of silicon process and packaging technologies. The automotive platform received considerable emphasis at the Symposium – this article specifically focuses on the… Read More

Highlights of the TSMC Technology Symposium 2021 – Packaging

The recent TSMC Technology Symposium provided several announcements relative to their advanced packaging offerings.

General

3DFabricTM

Last year, TSMC merged their 2.5D and 3D package offerings into a single, encompassing brand – 3DFabric.

2.5D package technology – CoWoS

The 2.5D packaging options are divided into the CoWoS… Read More

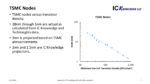

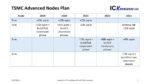

Highlights of the TSMC Technology Symposium 2021 – Silicon Technology

Recently, TSMC held their annual Technology Symposium, providing an update on the silicon process technology and packaging roadmap. This article will review the highlights of the silicon process developments and future release plans.

Subsequent articles will describe the packaging offerings and delve into technology … Read More

TSMC and the FinFET Era!

While there is a lot of excitement around the semiconductor shortage narrative and the fabs all being full, both 200mm and 300mm, there is one big plot hole and that is the FinFET era.

Intel ushered in the FinFET era only to lose FinFET dominance to the foundries shortly thereafter. In 2009 Intel brought out a 22nm FinFET wafer at the… Read More

TSMC 2021 Technical Symposium Actions Speak Louder Than Words

The TSMC Symposium kicked of today. I will share my general thoughts while Tom Dillinger will do deep dives on the technology side. The event started with a keynote by TSMC CEO CC Wei followed by technology presentations by the TSMC executive staff.

C.C. Wei introduced a new sound bite this year that really resonated with me and that… Read More

Is IBM’s 2nm Announcement Actually a 2nm Node?

IBM has announced the development of a 2nm process.

IBM Announcement

What was announced:

- “2nm”

- 50 billion transistors in a “thumbnail” sized area later disclosed to be 150mm2 = 333 million transistors per millimeter (MTx/mm2).

- 44nm Contacted Poly Pitch (CPP) with 12nm gate length.

- Gate All Around (GAA), there are several ways

How to Spend $100 Billion Dollars in Three Years

TSMC recently announced plans to spend $100 billion dollars over three years on capital. For 2021 they announced $30B in total capital with 80% on advanced nodes (7nm and smaller), 10% on packaging and masks and 10% on “specialty”.

If we take a guess at the capital for each year, we can project something like $30B for 2021 (announced),… Read More